# Complex Programmable Logic Devices

1997

Data Handbook IC27 CD-ROM included

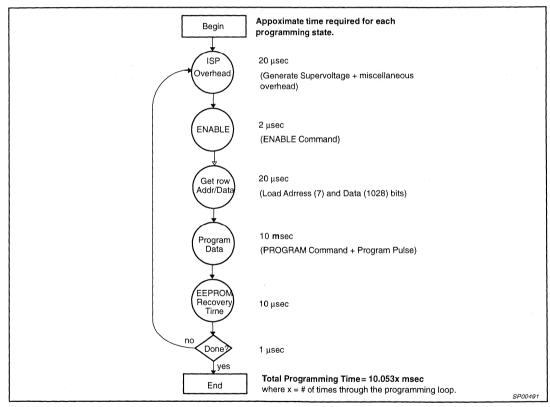

Let's make things better.

**PHILIPS**

# **QUALITY ASSURED**

Our quality system focuses on the continuing high quality of our components and the best possible service for our customers. We have a three-sided quality strategy: we apply a system of total quality control and assurance; we operate customer-oriented dynamic improvement programs; and we promote a partnering relationship with our customers and suppliers.

# **PRODUCT SAFETY**

In striving for state-of-the-art perfection, we continuously improve components and processes with respect to environmental demands. Our components offer no hazard to the environment in normal use when operated or stored within the limits specified in the data sheet.

Some components unavoidably contain substances that, if exposed by accident or misuse, are potentially hazardous to health. Users of these components are informed of the danger by warning notices in the data sheets supporting the components. Where necessary the warning notices also indicate safety precautions to be taken and disposal instructions to be followed. Obviously users of these components, in general the set-making industry, assume responsibility toward the consumer with respect to safety matters and environmental demands.

All used or obsolete components should be disposed of according to the regulations applying at the disposal location. Depending on the location, electronic components are considered to be 'chemical,' 'special' or sometimes 'industrial' waste. Disposal as domestic waste is usually not permitted.

# Complex Programmable Logic Devices (CPLDs)

# **CONTENTS**

|           |                                      | page |

|-----------|--------------------------------------|------|

|           | PREFACE                              | 3    |

| SECTION 1 | GENERAL INFORMATION                  | 5    |

| SECTION 2 | INTRODUCTION                         | 19   |

| SECTION 3 | IN-SYSTEM PROGRAMMING (ISP $^{TM}$ ) | 41   |

| SECTION 4 | CPLD DATASHEETS                      | 57   |

| SECTION 5 | RELATED PRODUCTS                     | 163  |

| SECTION 6 | APPLICATION NOTES                    | 187  |

| SECTION 7 | PACKAGE INFORMATION                  | 405  |

| SECTION 8 | DATA HANDBOOK SYSTEM                 | 419  |

### **DEFINITIONS**

| Data Sheet Identification | Product Status         | Definition (Note)                                                                                                                                                                                                                                          |

|---------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Objective Specification   | Formative or in Design | This data sheet contains the design target or goal specifications for product development. Specifications may change in any manner without notice.                                                                                                         |

| Preliminary Specification | Preproduction Product  | This data sheet contains preliminary data, and supplementary data will be published at a later date. Philips Semiconductors reserves the right to make changes at any time without notice in order to improve design and supply the best possible product. |

| Product Specification     | Full Production        | This data sheet contains Final Specifications. Philips Semiconductors reserves the right to make changes at any time without notice, in order to improve design and supply the best possible product.                                                      |

| Short-form specification  | _                      | The data in this specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.                                                                             |

# Limiting values

Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

# **Application information**

Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification

### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such improper use or sale.

### **DISCLAIMER**

Philips Semiconductors reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

**NOTE:** Always check with your local Philips Semiconductors Sales Office to be certain that you have the latest data sheet(s) before completing a design.

# **Preface**

# Introducing the only high-speed, zero-power CPLD solution

Sustaining a competitive edge in the high-performance arena requires you to maximize speed, minimize power use, and deliver more functionality—for both portable and mainstream PLD applications.

Philips Semiconductors gives you this edge with a superior solution that combines, for the first time ever, high speed and zero power into a CPLD. Using exclusive Philips technologies, including eXtended Programmable Logic Array (XPLA™), Fast Zero Power (FZP™), and standard In-System Programmability (ISP™), Philips has created new CPLD families. The families consist of ten devices in two process technologies across fifteen package types. Each solution offers you higher levels of integration than the competition, without sacrificing performance.

To ensure an easy-to-use CPLD solution, Philips offers world class software and application support. To enhance the support package, key partnerships with Synario Design Automation, Minc, IsData, and others have been formed to ensure state-of-the-art design solutions that are easily accessible to the designer. Whether it be Synario, Minc, Cadence, Viewlogic, Mentor or Synopsys, Philips provides design flows that allow you to complete designs on schedule.

# Philips delivers the broadest range of 3V/5V CPLD solutions across all densities

The XPLA architecture serves as the foundation for all Philips' CPLD families. Current Philips CPLDs accommodate applications demanding industry-standard 32, 64 and 128 macrocell densities. As the demand for faster, larger, more power-efficient applications grows, future XPLA product families will use a combination of low-power techniques and state-of-the-art processing to extend densities up to 1,000 macrocells and beyond.

## Now you can maximize density without sacrificing speed

Philips' new XPLA provides an architecture that enables you to efficiently allocate logic for 100% utilization without sacrificing speed. The XPLA provides a fast path to every macrocell, which includes five dedicated PAL product terms. Plus the XPLA's PLA structure and predictable sharing access times make it the fastest and most flexible solution available. Because the XPLA allocates additional logic exactly where you need it, it delivers key benefits competitive devices cannot. Benefits include no stealing of logic from neighbor macrocells, no density loss when sharing logic, no lost logic due to product-term granularity problems, no slow feedback logic, and no refitting or routing problems.

## Philips shatters the myth—zero power no longer means slow speeds

With propagation delays of just 8ns at 3V and 6ns at 5V, and standby currents under 100 microamps, Philips' new FZP technology stands alone in breaking the paradigm that zero power equals slow speeds. When compared to today's standard zero power devices, with propagation delays of 20–25ns, Philips' CPLDs with FZP boast a 250% to 300% faster operating speed. And because no turbo-bits or sleep-modes are used, these CPLDs offer zero static power and low dynamic power all the time.

1997 Mar 21 3

# TRADEMARK LIST

Altera 7000 series devices PLDSynthesis II™

CoolRunner™ Quicksim II

FZP™ SpeedWave™

Autol ogic™ Sun MicroSystems SunOS

AutoLogic<sup>™</sup> Sun MicroSystems SunOS

Cadence PIC Designer<sup>™</sup> Sun MicroSystems Solaris

Concept™ Synario

Composer™ Synergy™

Design Architect™ Synopsys®

Verilog XI ™

$DSL^{TM}$  Verilog-XL<sup>TM</sup> ISPTM ViewPLD®

Hewlett-Packard HP-UX 9.05 ViewDraw®

Intel ViewSynthesis®

Intelliflow™ ViewSim®

Leapfrog™ Windows®95

Mentor Design Architect Windows NT®

Mentor Graphics Idea Station® XPLA™

<sup>™, ®</sup> Product and Company names are registered trademarks of their respective organizations.

# Section 1 General Information

### CONTENTS

| CONTENTS                         | <br>6  |

|----------------------------------|--------|

| Family Selection Guide           | <br>8  |

| Ordering Information             | <br>11 |

| FAX-on-DEMAND System             | <br>13 |

| CPLD internet and support access | <br>15 |

| Handling MOS devices             | <br>17 |

| Quality                          | 10     |

# **CONTENTS**

|                   | x Programmable Logic Devices (CPLDs)                                                        |

|-------------------|---------------------------------------------------------------------------------------------|

| Prelace           |                                                                                             |

| Section 1 - Gen   |                                                                                             |

| CONTENTS          |                                                                                             |

| Family Selection  | Guide                                                                                       |

| Ordering Informa  | tion                                                                                        |

| FAX-on-DEMAN      | D System                                                                                    |

|                   | nd support access                                                                           |

| Handling MOS d    | evices                                                                                      |

| Quality           |                                                                                             |

| Section 2 – Intro | duction                                                                                     |

| XPLA™ architect   | ure                                                                                         |

| Fast Zero Power   | (FZP™)                                                                                      |

| Development so    | ftwareftware                                                                                |

| Programming co    | mpanies                                                                                     |

| Section 3 - In-S  | ystem Programming (ISP™)                                                                    |

| In-System Progr   | amming (ISP <sup>TM</sup> )                                                                 |

| ISP Download C    | able Specification                                                                          |

| 101 Download C    | able openinoalion                                                                           |

| Section 4 - CPL   |                                                                                             |

| PZ3032            | 32 macrocell CPLD                                                                           |

| PZ5032            | 32 macrocell CPLD                                                                           |

| PZ3064            | 64 macrocell CPLD                                                                           |

| PZ5064            | 64 macrocell CPLD                                                                           |

| PZ3128            | 128 macrocell CPLD                                                                          |

| PZ5128            | 128 macrocell CPLD                                                                          |

| PZ3128-10         | 128 macrocell CPLD                                                                          |

| PZ5128-7          | 128 macrocell CPLD                                                                          |

| Section 5 – Rela  | ted products                                                                                |

| P3Z22V10          | 3V zero power, TotalCMOS™, universal PLD device                                             |

| P5Z22V10          | 5V zero power, TotalCMOS™, universal PLD device                                             |

| Section 6 Ann     | lication notes                                                                              |

| Section 6 – App   |                                                                                             |

| AN055             | Metastability characteristics for Philips CPLDs – PZ3032                                    |

| AN056             | Metastability characteristics for Philips CPLDs – PZ5032                                    |

| AN057             | Altera (AHDL) to Phillips (PHDL) design conversion guidelines                               |

| AN058             | Cadence/Synopsys design flows for targeting Phillips CPLDs                                  |

| AN059             | Mentor Graphics design flow for targeting Philips Semiconductors CPLDs                      |

| AN060             | Using Data I/O model technology PC-based VHDL tools to target Phillips Semiconductors CPLDs |

| AN061             | XPLA Designer workstation flow for targeting Philips CPLDs                                  |

| AN062             | Understanding the hidden costs of using high–power CPLDs                                    |

| AN063             | Probing internal nodes using XPLA Designer's graphic simulator                              |

| AN064             | Using sum of products control terms in Philips CoolRunner™ CPLDs                            |

| AN065             | Understanding CoolRunner™ clocking options                                                  |

| AN066             | XPLA Designer™ hierarchical PHDL design support                                             |

| AN067             | JEDEC file equation generator                                                               |

| AN068             | Terminating unused CoolRunner™ I/O pins                                                     |

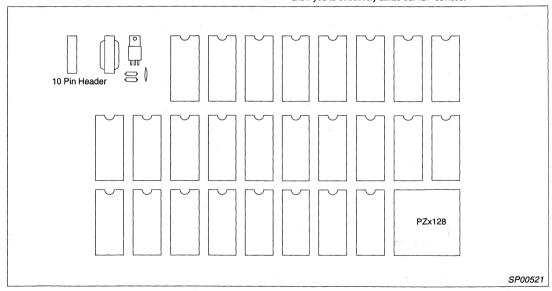

| AN069             | ISP design considerations for the CoolRunner™ PZx128 CPLD                                   |

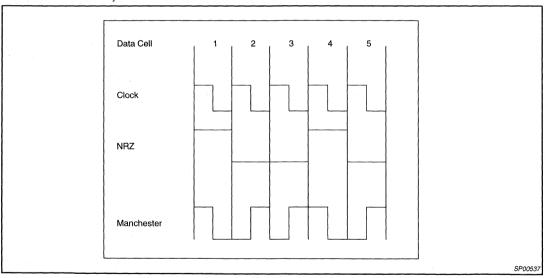

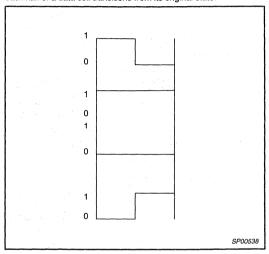

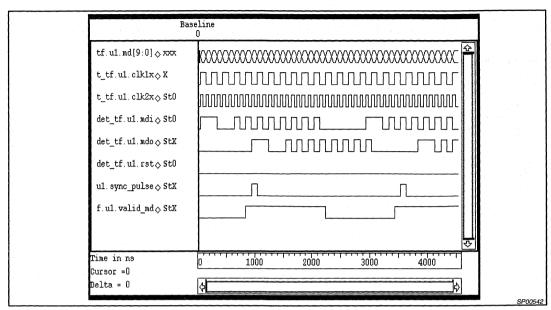

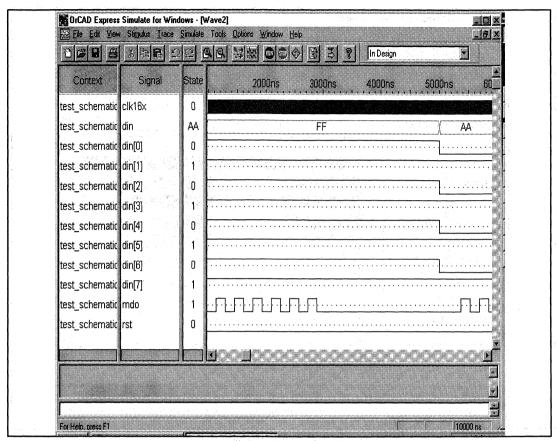

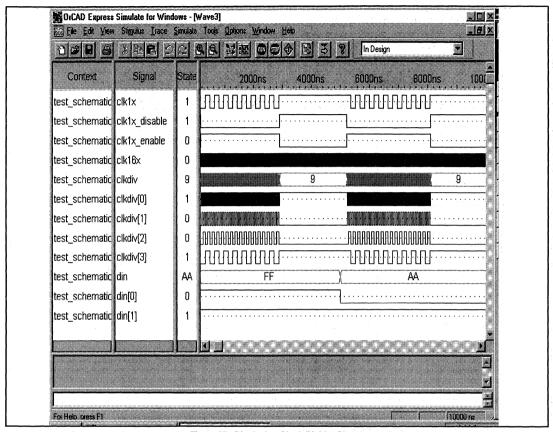

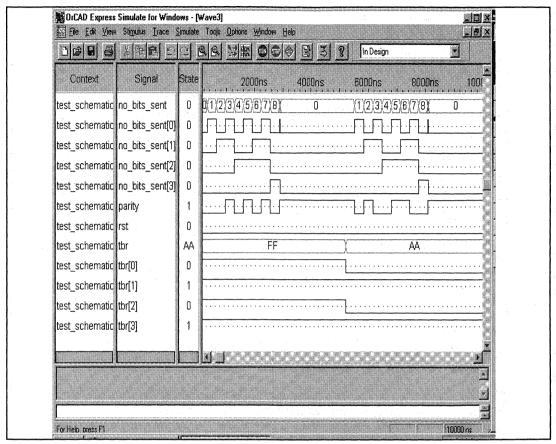

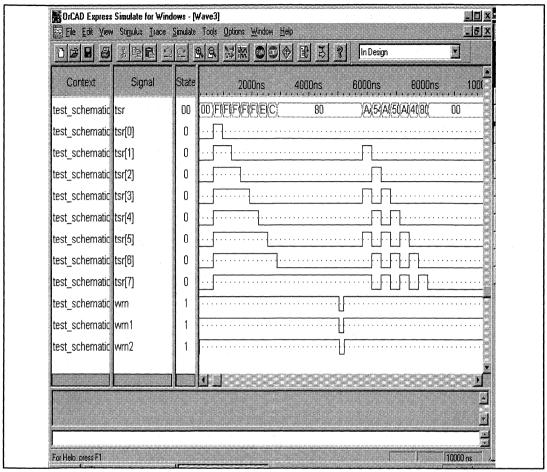

| AN070             | Verilog implementation of a Manchester Encoder/Decoder in Philips CPLDs                     |

| AN071             | OrCad express—Minc PLDesigner flow for Philips CPLDs                                        |

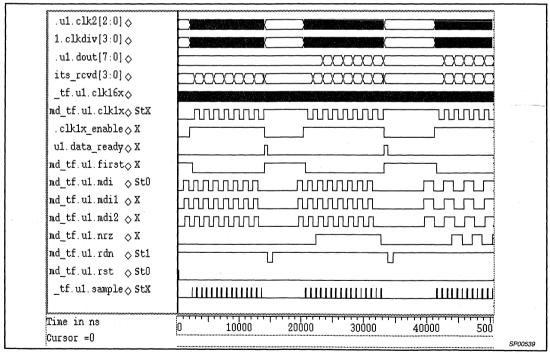

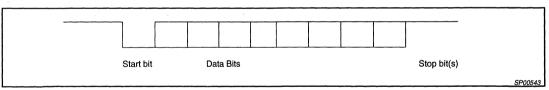

| AN072             | Implementing a UART in Philips CPLDs                                                        |

| AN073             | Synplicity/Model Tech design flow for targeting Philips CPLDs                               |

| Section 7 - Pac   | kage information                                                                            |

|                   | rage information                                                                            |

|                   |                                                                                             |

# **CONTENTS**

| Package outlines                                                                                                        |               |          |           |

|-------------------------------------------------------------------------------------------------------------------------|---------------|----------|-----------|

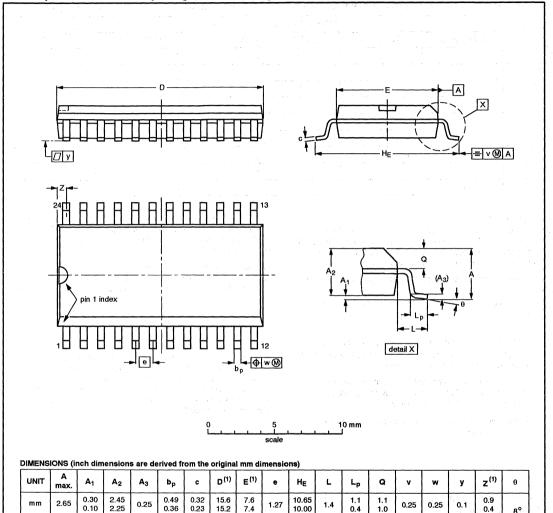

| SO24: plastic small outline package; 24 leads; body width 7.5 mm                                                        |               | COT127.1 | 408       |

| TSSOP24: plastic small outline package; 24 leads; body width 4.4 m                                                      |               |          | 409       |

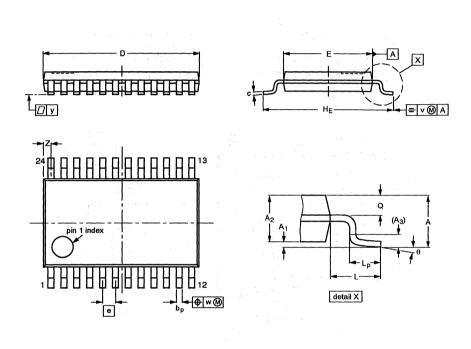

| PLCC28: plastic leaded chip carrer; 28 leads; pedestal                                                                  |               |          | 410       |

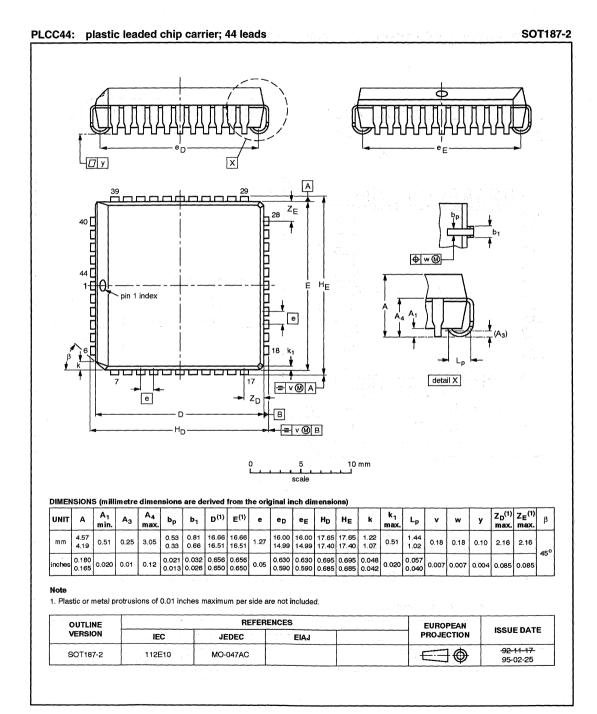

| PLCC44: plastic leaded chip carrier; 44 leads                                                                           |               |          | 411       |

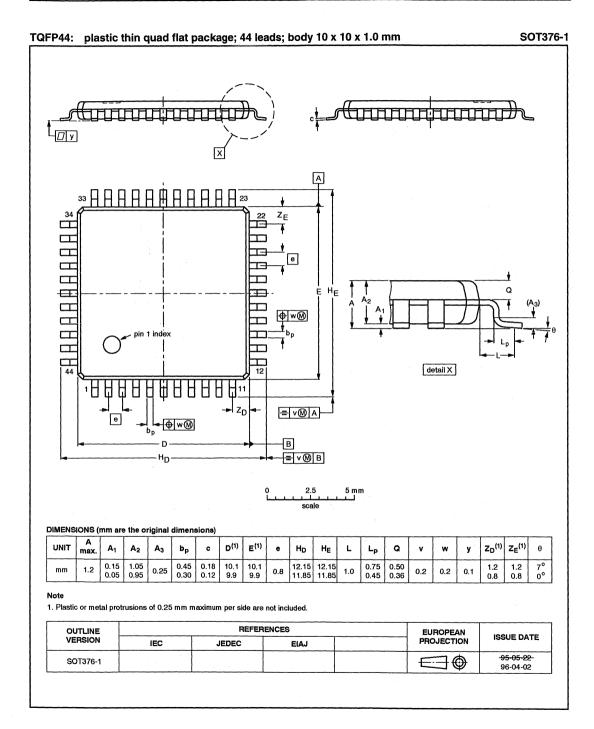

| TQFP44: plastic thin quad flat package; 44 leads; body 10 x 10 x 1.0 mm                                                 |               | SOT376-1 | <br>412   |

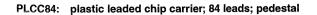

| PLCC68: plastic leaded chip carrier; 68 leads; pedestal                                                                 |               |          | 413       |

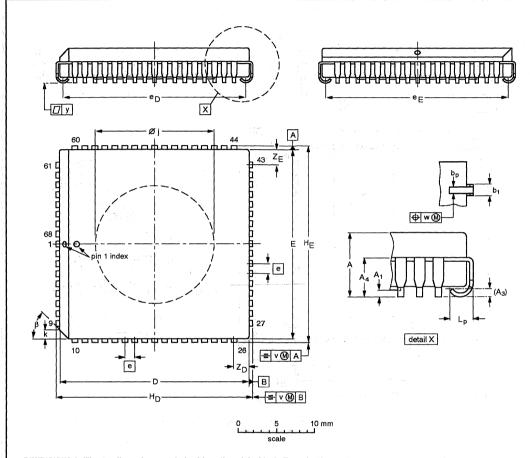

| PLCC84: plastic leaded chip carrier; 84 leads; pedestal                                                                 |               | SOT189-3 | <br>414   |

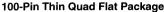

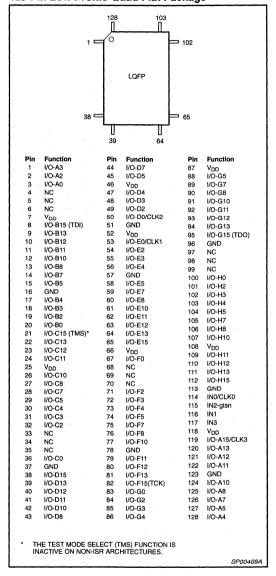

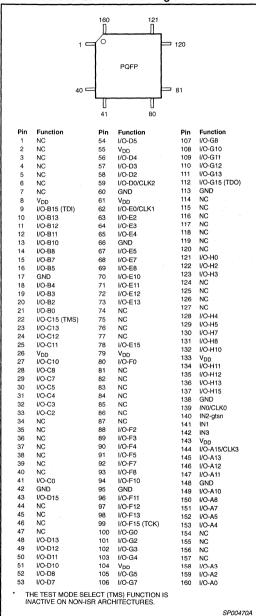

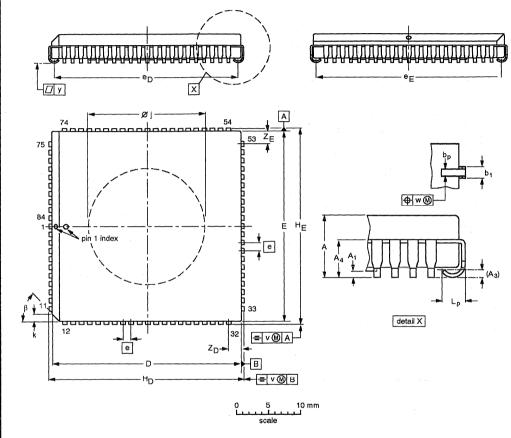

| QFP100: plastic quad flat package; 100 leads (lead length 1.6 mm); body 14 >                                            | x 20 x 2.8 mm | SOT382-1 | <br>415   |

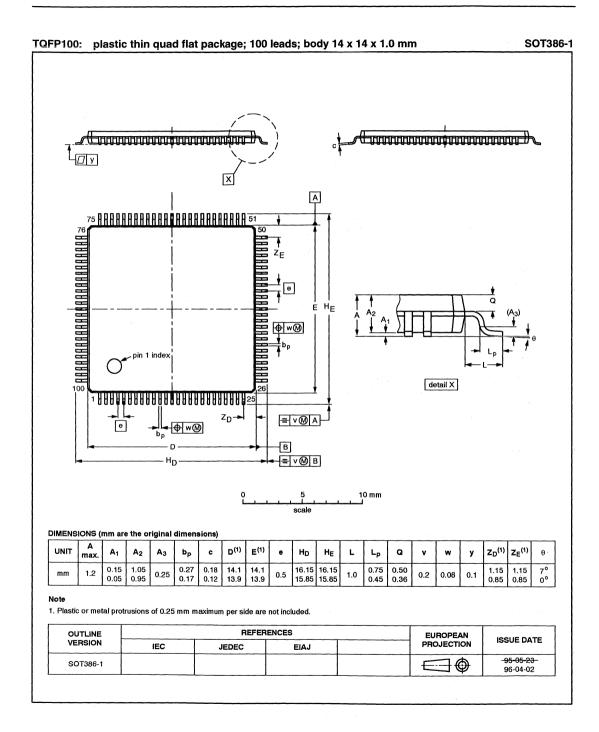

| TQFP100: plastic thin quad flat package; 100 leads; body 14 x 14 x 1.0 mm                                               |               |          | 416       |

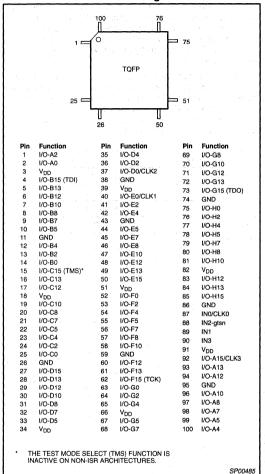

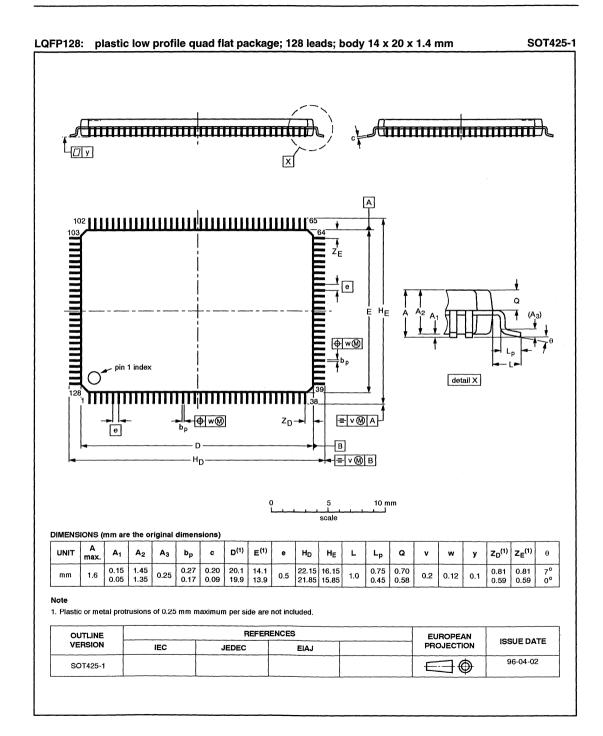

| LQFP128: plastic low profile quad flat package; 128 leads; body 14 x 20 x 1.4 r                                         | mm            | SOT425-1 | <br>417   |

|                                                                                                                         |               |          |           |

| Data Handbook system                                                                                                    |               |          | <br>. 420 |

|                                                                                                                         |               |          |           |

| ADDITIONAL MATERIAL ON ENCLOSED CD-ROM ONLY:                                                                            |               |          |           |

| Application Notes/Design Models                                                                                         |               |          |           |

| Verilog models of commonly used digital function for targeting Philips CPLDs                                            |               |          |           |

| VHDL models of commonly used digital functions for targeting Philips CPLDs                                              |               |          |           |

| Philips hardware description language models of commonly used digital functions                                         |               |          |           |

| Exemplar/Model tech design flow for targeting Philips CPLDs                                                             |               |          |           |

| A Perl utility for converting Altera 7000 series into Philips CPLDs                                                     |               |          |           |

| Eight bit shift register                                                                                                |               |          |           |

| Adders                                                                                                                  |               |          |           |

| N-bit adder                                                                                                             |               |          |           |

| Eight bit adder                                                                                                         |               |          |           |

| Low level implementation of 8 bit adder                                                                                 |               |          |           |

| Four bit adder with carry in and carry out                                                                              |               |          |           |

| BCD to seven segment decoder/driver with active low outputs                                                             |               |          |           |

| Eight bit comparator – high level implementation                                                                        |               |          |           |

| Counters                                                                                                                |               |          |           |

| 16 bit counter – low level implementation                                                                               |               |          |           |

| Two 16 bit up/down/loadable/enabled/resettable counters Four bit up/down/loadable counter with bi-directional load pins |               |          |           |

| 16 bit gray code counter                                                                                                |               |          |           |

| Four bit gray code counter                                                                                              |               |          |           |

| Prep 2 – Two 8 bit loadable registers, mux, counter, and comparator                                                     |               |          |           |

| Prep 7 – 16 bit loadable binary counter – 2 reps                                                                        |               |          |           |

| Prep 8 – 16 bit synchronous prescaled counter – 2 reps                                                                  |               |          |           |

| Serial CRC generator using LFSR $g(x) = x16 + x12 + x5 + 1$                                                             |               |          |           |

| 3 to 8 decoder                                                                                                          |               |          |           |

| 8 bit loadable data register                                                                                            |               |          |           |

| DRAM controller for a R3081E microprocessor                                                                             |               |          |           |

| Combinatorial method of implementing divide-by-N                                                                        |               |          |           |

| High level implementation of a 16-to-8 multiplexer                                                                      |               |          |           |

| Dual 4-to-1 multiplexer                                                                                                 |               |          |           |

| Ring oscillator with divide                                                                                             |               |          |           |

| Prep 1 – Datapath circuit – 2 reps                                                                                      |               |          |           |

| 8 bit mux feeds 8 bit data reg, which feeds 8 bit shift register                                                        |               |          |           |

| Prep 3 – 3 reps                                                                                                         |               |          |           |

| Small state machine – 8 inputs, 8 registered outputs                                                                    |               |          |           |

| Prep 5 – Arithmetic circuit                                                                                             |               |          |           |

| 4×4 multiplier, 8 bit adder, 8 bit register  Prep 6 – One 16 bit accumulator                                            |               |          |           |

| Prep 9 – One 16 bit accumulator  Prep 9 – 3 reps                                                                        |               |          |           |

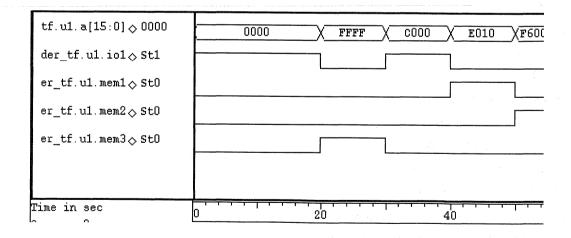

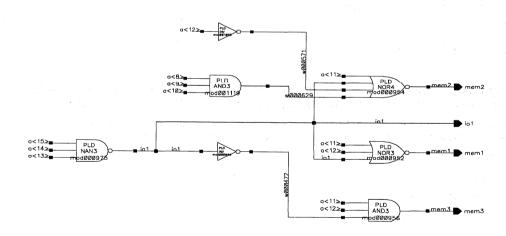

| Memory mapped I/O address decoder                                                                                       |               |          |           |

| 8 bit fast parity generator                                                                                             |               |          |           |

| DRAM refresh counter                                                                                                    |               |          |           |

|                                                                                                                         |               |          |           |

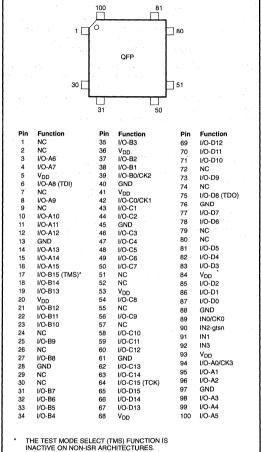

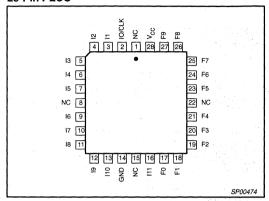

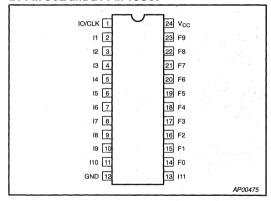

# **Device pinouts**

Dual ring oscillators

# **Family Selection Guide**

# PHILIPS CoolRunner TM FAMILY SELECTION GUIDE – COMMERCIAL TEMP RANGE (0 TO $+70^{\circ}$ C)

| Part<br>Number | Package(s)                                                                  | Pkg<br>Designator              | Macrocells | Gates | ls &<br>I/Os    | Buried<br>Macro<br>cells | t <sub>PD</sub> | Iddq  | lddd<br>@1MHz | Supply<br>Voltage |

|----------------|-----------------------------------------------------------------------------|--------------------------------|------------|-------|-----------------|--------------------------|-----------------|-------|---------------|-------------------|

| PZ3032         | 44 pin PLCC<br>44 pin TQFP                                                  | A44<br>BC                      | 32         | 1000  | 36              | 0                        | 8, 10, 12       | 35μΑ  | 0.5mA         | 3.0 – 3.3V        |

| PZ5032         | 44 pin PLCC<br>44 pin TQFP                                                  | A44<br>BC                      | 32         | 1000  | 36              | -, 0                     | 6, 7.5, 10      | 75μΑ  | 3mA           | 4.75 – 5.25V      |

| PZ3064         | 44 pin PLCC<br>44 pin TQFP<br>68 pin PLCC<br>84 pin PLCC<br>100 pin PQFP    | A44<br>BC<br>A68<br>A84<br>BB1 | 64         | 2000  | 36<br>52<br>68  | 32<br>16<br>0            | 10, 12          | 50μΑ  | 1mA           | 3.0 – 3.3V        |

| PZ5064         | 44 pin PLCC<br>44 pin TQFP<br>68 pin PLCC<br>84 pin PLCC<br>100 pin PQFP    | A44<br>BC<br>A68<br>A84<br>BB1 | 64         | 2000  | 36<br>52<br>68  | 32<br>16<br>0            | 7.5, 10         | 80μΑ  | 3mA           | 4.75 – 5.25 V     |

| PZ3128         | 84 pin PLCC<br>100 pin PQFP<br>100 pin TQFP<br>128 pin LQFP<br>160 pin PQFP | A84<br>BB1<br>BP<br>BE<br>BB2  | 128        | 4000  | 68<br>84<br>100 | 64<br>48<br>32           | 10, 12, 15      | 60μΑ  | 2mA           | 3.0 – 3.3V        |

| PZ5128         | 84 pin PLCC<br>100 pin PQFP<br>100 pin TQFP<br>128 pin LQFP<br>160 pin PQFP | A84<br>BB1<br>BP<br>BE<br>BB2  | 128        | 4000  | 68<br>84<br>100 | 64<br>48<br>32           | 7.5, 10, 12     | 100μΑ | 5mA           | 4.75 – 5.25 V     |

1997 Jun 16 8

# Family Selection Guide

# PHILIPS CoolRunner™ FAMILY SELECTION GUIDE - INDUSTRIAL TEMP RANGE (-40 TO +85°C)

| Part<br>Number | Package(s)                                                                  | Pkg<br>Designator              | Macrocells | Gates | Is &<br>I/Os    | Buried<br>Macro<br>cells | t <sub>PD</sub> | lddq  | lddd<br>@1MHz | Supply<br>Voltage |

|----------------|-----------------------------------------------------------------------------|--------------------------------|------------|-------|-----------------|--------------------------|-----------------|-------|---------------|-------------------|

| PZ3032I        | 44 pin PLCC<br>44 pin TQFP                                                  | A44<br>BC                      | 32         | 1000  | 36              | 0                        | 10, 12          | 45μΑ  | 0.5mA         | 3.0 – 3.3V        |

| PZ5032I        | 44 pin PLCC<br>44 pin TQFP                                                  | A44<br>BC                      | 32         | 1000  | 36              | 0                        | 7.5, 10         | 95μΑ  | 4mA           | 4.5 – 5.5V        |

| PZ3064I        | 44 pin PLCC<br>44 pin TQFP<br>68 pin PLCC<br>84 pin PLCC<br>100 pin PQFP    | A44<br>BC<br>A68<br>A84<br>BB1 | 64         | 2000  | 36<br>52<br>68  | 32<br>16<br>0            | 12, 15          | 50μΑ  | 1mA           | 3.0 – 3.3V        |

| PZ5064I        | 44 pin PLCC<br>44 pin TQFP<br>68 pin PLCC<br>84 pin PLCC<br>100 pin PQFP    | A44<br>BC<br>A68<br>A84<br>BB1 | 64         | 2000  | 36<br>52<br>68  | 32<br>16<br>0            | 10, 12          | 100μΑ | 4mA           | 4.5 – 5.5 V       |

| PZ3128I        | 84 pin PLCC<br>100 pin PQFP<br>100 pin TQFP<br>128 pin LQFP<br>160 pin PQFP | A84<br>BB1<br>BP<br>BE<br>BB2  | 128        | 4000  | 68<br>84<br>100 | 64<br>48<br>32           | 15, 20          | 75μΑ  | 3mA           | 3.0 – 3.3V        |

| PZ5128I        | 84 pin PLCC<br>100 pin PQFP<br>100 pin TQFP<br>128 pin LQFP<br>160 pin PQFP | A84<br>BB1<br>BP<br>BE<br>BB2  | - 128      | 4000  | 68<br>84<br>100 | 64<br>48<br>32           | 12, 15          | 125μΑ | 6mA           | 4.5 – 5.5 V       |

1997 Jun 16

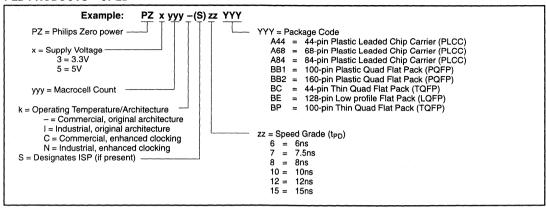

# **Ordering Information**

# PLD PRODUCTS - CPLD

April 1997 11

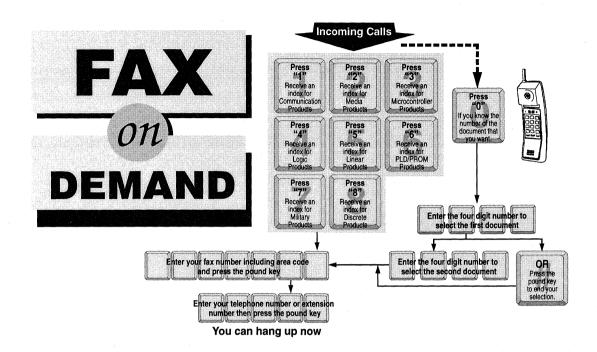

# **FAX-on-DEMAND System**

# What is it?

The FAX-on-DEMAND system is a computer facsimile system that allows customers to receive selected documents by fax automatically.

# How does it work?

To order a document, you simply enter the document number. This number can be obtained by asking for an index of available documents to be faxed to you the first time you call the system.

Our system has a selection of the latest product data sheets from Philips with varying page counts. As you know, it takes approximately one minute to FAX one page. This isn't bad if the number of pages is less than 10. But if the document is 37 pages long, be ready for a long transmission!

Philips Semiconductors also maintains product information on the World-Wide Web. Our home page can be located at:

http://www.semiconductors.philips.com

# Who do I contact if I have a question about FAX-on-DEMAND?

Contact your local Philips sales office.

# **FAX-on-DEMAND** phone numbers:

England (United Kingdom, Ireland) 44-181-730-5020 (United Kingdom, Ireland) 33-1-40-99-60-60 Italy 39-167-295502

1-800-282-2000

# Locations soon to be in operation:

Hong Kong Japan The Netherlands

North America

1997 Mar 04 13

# **CPLD** internet and support access

# **INTERNET ACCESS**

# **Philips Semiconductors World Wide Web:**

http://www.semiconductors.philips.com

# Philips CPLD World Wide Web:

http://www.coolpld.com

# **Email CPLD Support Address:**

coolpld@abq.sc.philips.com

1997 Apr 18 15

# General

# Handling MOS devices

### **FLECTROSTATIC CHARGES**

Electrostatic charges can exist in many things; for example, man-made-fibre clothing, moving machinery, objects with air blowing across them, plastic storage bins, sheets of paper stored in plastic envelopes, paper from electrostatic copying machines, and people. The charges are caused by friction between two surfaces, at least one of which is non-conductive. The magnitude and polarity of the charges depend on the different affinities for electrons of the two materials rubbing together, the friction force and the humidity of the surrounding air.

Electrostatic discharge is the transfer of an electrostatic charge between bodies at different potentials and occurs with direct contact or when induced by an electrostatic field. All of our MOS devices are internally protected against electrostatic discharge but they can be damaged if the following precautions are not taken.

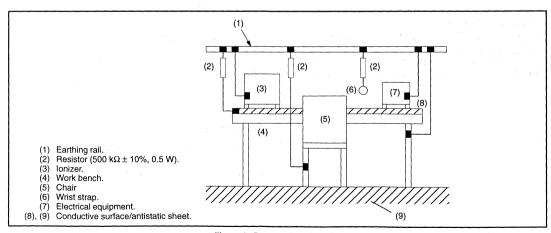

### WORK STATION

Figure 1 shows a working area suitable for safely handling electrostatic sensitive devices. It has a work bench, the surface of which is conductive or covered by an antistatic sheet. Typical resistivity for the bench surface is between 1 and 500 k $\Omega$  per cm². The floor should also be covered with antistatic material. The following precautions should be observed:

- Persons at a work bench should be earthed via a wrist strap and a resistor

- All mains-powered electrical equipment should be connected via an earth leakage switch

- · Equipment cases should be earthed

- Relative humidity should be maintained between 50 and 65%

- An ionizer should be used to neutralize objects with immobile static charges

### RECEIPT AND STORAGE

MOS devices are packed for dispatch in antistatic/conductive containers, usually boxes, tubes or blister tape. The fact that the

contents are sensitive to electrostatic discharge is shown by warning labels on both primary and secondary packing.

The devices should be kept in their original packing whilst in storage. If a bulk container is partially unpacked, the unpacking should be performed at a protected work station. Any MOS devices that are stored temporarily should be packed in conductive or antistatic packing or carriers.

### **ASSEMBLY**

MOS devices must be removed from their protective packing with earthed component pincers or short-circuit clips. Short-circuit clips must remain in place during mounting, soldering and cleansing/drying processes. Do not remove more devices from the storage packing than are needed at any one time. Production/assembly documents should state that the product

Production/assembly documents should state that the product contains electrostatic sensitive devices and that special precautions need to be taken.

During assembly, endure that the MOS devices are the last of the components to be mounted and that this is done at a protected work station.

All tools used during assembly, including soldering tools and solder baths, must be earthed. All hand tools should be of conductive or antistatic material and, where possible, should not be insulated.

Measuring and testing of completed circuit boards must be done at a protected work station. Place the soldered side of the circuit board on conductive or antistatic foam and remove the short-circuit clips. Remove the circuit board from the foam, holding the board only at the edges. Make sure the circuit board does not touch the conductive surface of the work bench. After testing, replace the circuit board on the conductive foam to await packing.

Assembled circuit boards containing MOS devices should be handled in the same way a unmounted MOS devices, they should also carry waning labels and be packed in conductive or antistatic packing.

Figure 1. Protected work station

November 1994 17

General Quality

### TOTAL QUALITY MANAGEMENT

Philips Semiconductors is a Quality Company, renowned for the high quality of our products and service. We keep alive this tradition by constantly aiming towards one ultimate standard, that of zero defects. This aim is guided by our Total Quality Management (TQM) system, the basis of which is described in the following paragraphs.

### Quality assurance

Based on ISO 9000 standards, customer standards such as Ford TQE and IBM MDQ. Our factories are certified to ISO 9000 by external inspectorates.

## Partnerships with customers

PPM co-operations, design-in agreements, ship-to-stock, just-in-time and self-qualification programmes, and application support.

# Partnerships with suppliers

Ship-to-stock, statistical process control and ISO 9000 audits.

### Quality improvement programme

Continuous process and system improvement, design improvement, complete use of statistical process control, realization of our final objective of zero defects, and logistics improvement by ship-to-stock and just-in-time agreements.

### ADVANCED QUALITY PLANNING

During the design and development of new products and processes, quality is built-in by advanced quality planning. Through failure-mode-and-effect analysis the critical parameters are detected and measures taken to ensure good performance on these parameters. The capability of process steps is also planned in this phase.

### PRODUCT CONFORMANCE

The assurance of product conformance is an integral part of our quality assurance (QA) practice. This is achieved by:

- Incoming material management through partnerships with suppliers.

- In-line quality assurance to monitor process reproducibility during manufacture and initiate any necessary corrective action. Critical process steps are 100% under statistical process control.

- Acceptance tests on finished products to verify conformance with the device specification. The test results are used for quality feedback and corrective actions. The inspection and test requirements are detailed in the general quality specifications.

- Periodic inspections to monitor and measure the conformance of products.

### PRODUCT RELIABILITY

With the increasing complexity of Original Equipment Manufacturer (OEM) equipment, components reliability must be extremely high. Our research laboratories and development departments study the failure mechanisms of semiconductors. Their studies result in design rules and process optimization for the highest built-in product reliability. Highly accelerated tests are applied to the product reliability evaluation. Rejects from reliability tests and from customer complaints are submitted to failure analysis, to result in corrective action.

### **CUSTOMER RESPONSES**

Our quality improvement depends on joint action with our customer. We need our customer's inputs and we invite constructive comments on all aspects of our performance. Please contact our local sales representative.

# RECOGNITION

The high quality of our products and services is demonstrated by many Quality Awards granted by major customers and international organizations.

1995 Mar 21

# **Philips Semiconductors**

# Section 2 Introduction

# CONTENTS

| (PLA™ architecture    | 21 |

|-----------------------|----|

| ast Zero Power (FZP™) |    |

| Development software  | 29 |

| Programming companies | 39 |

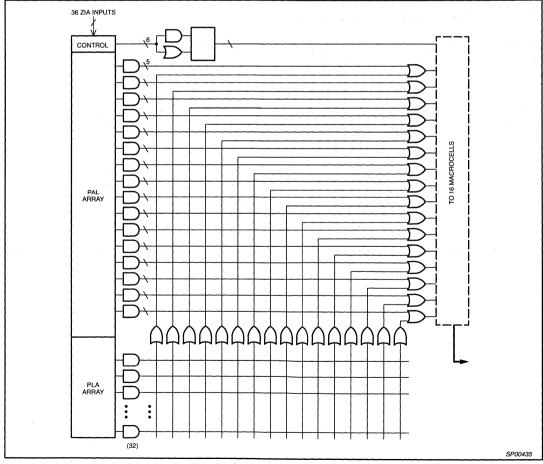

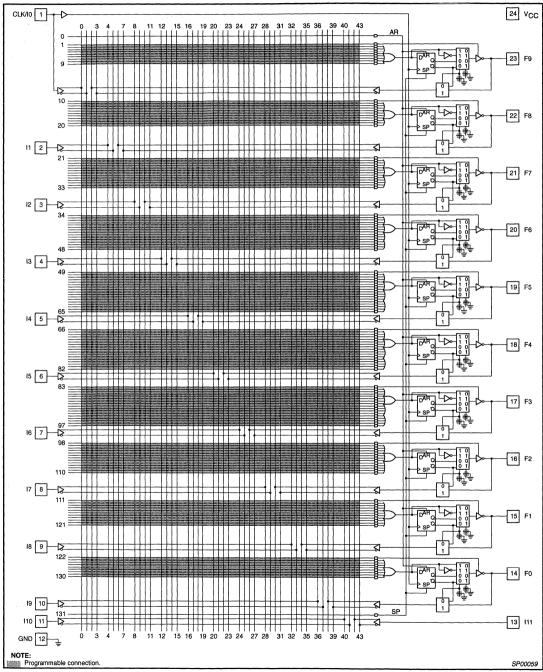

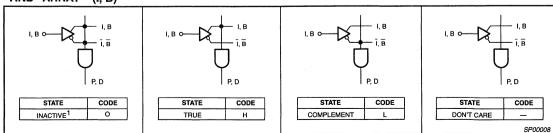

### XPLA™ ARCHITECTURE

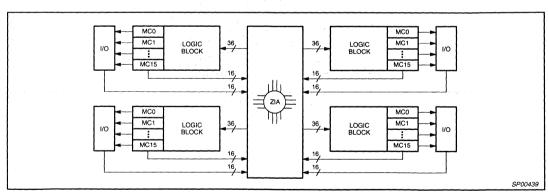

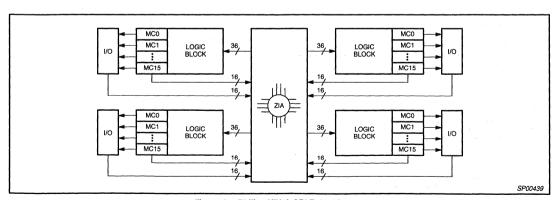

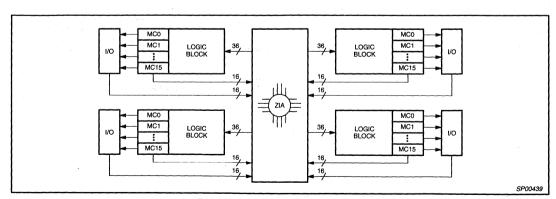

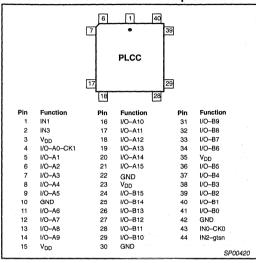

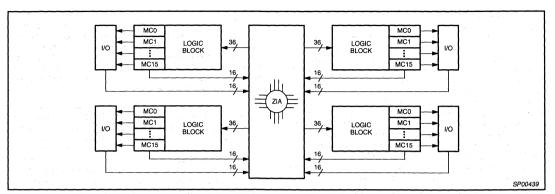

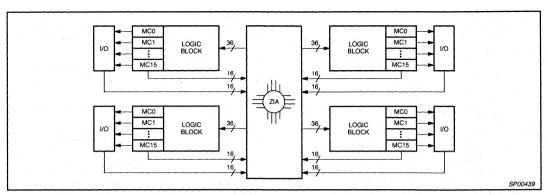

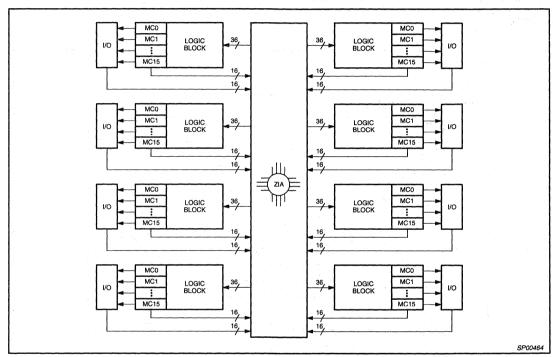

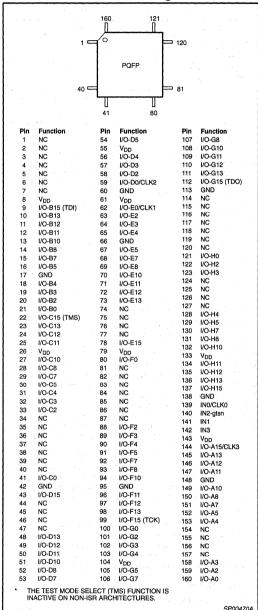

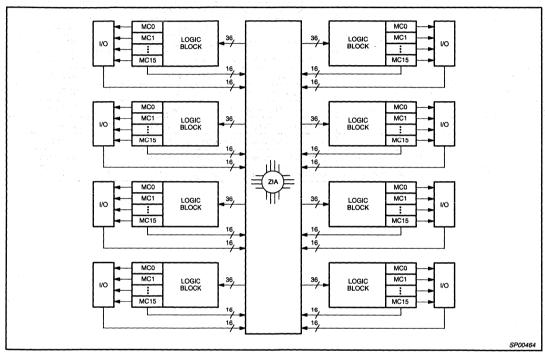

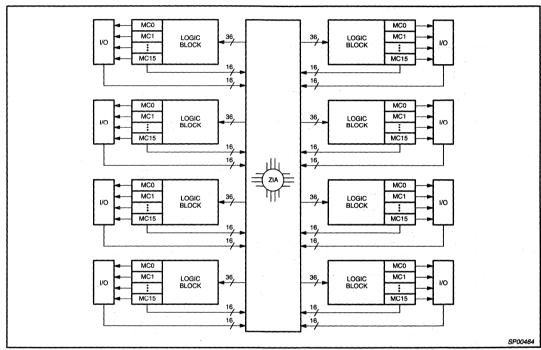

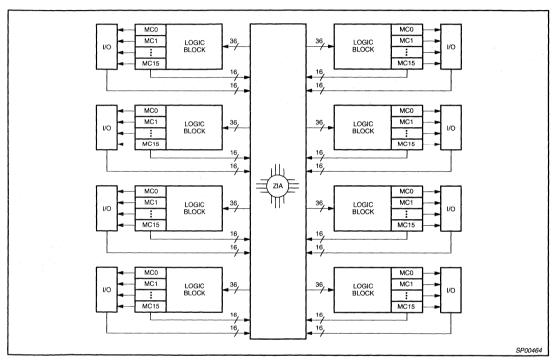

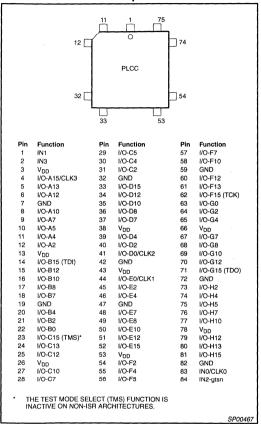

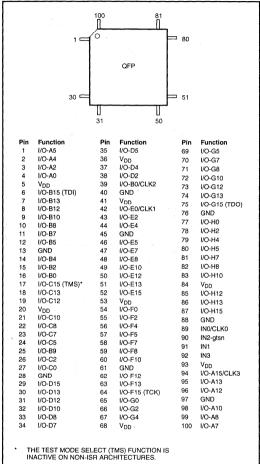

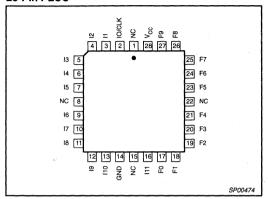

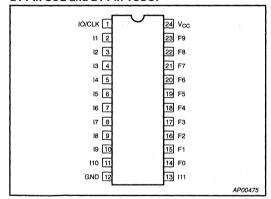

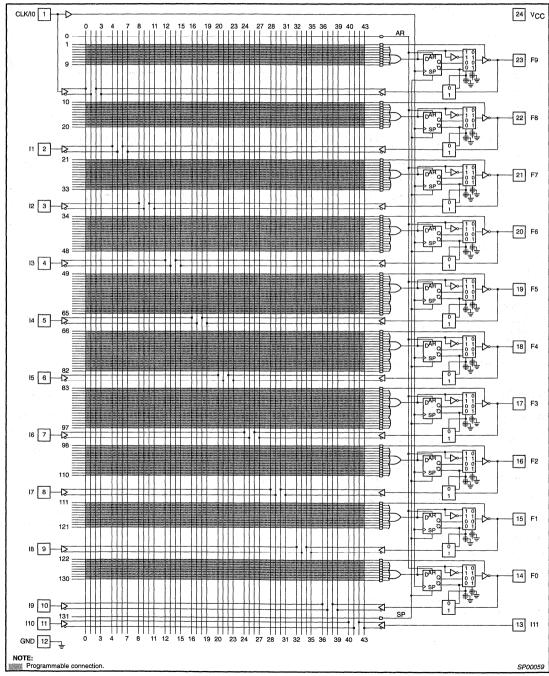

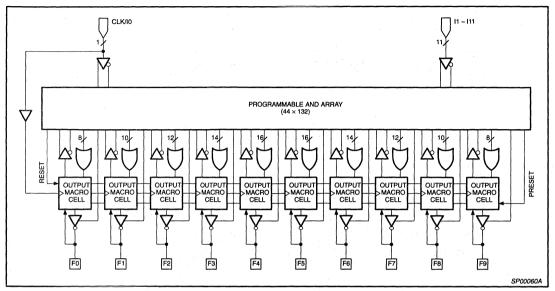

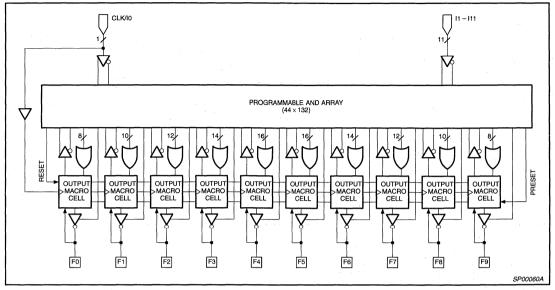

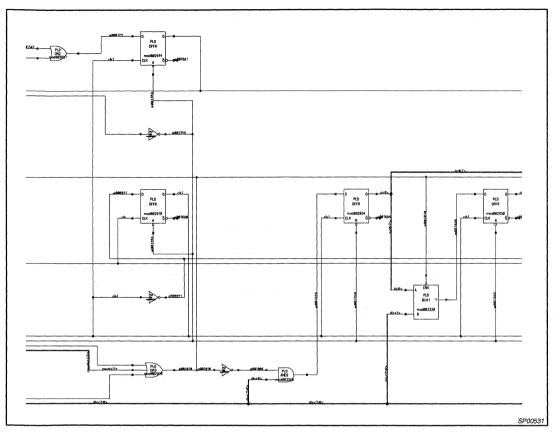

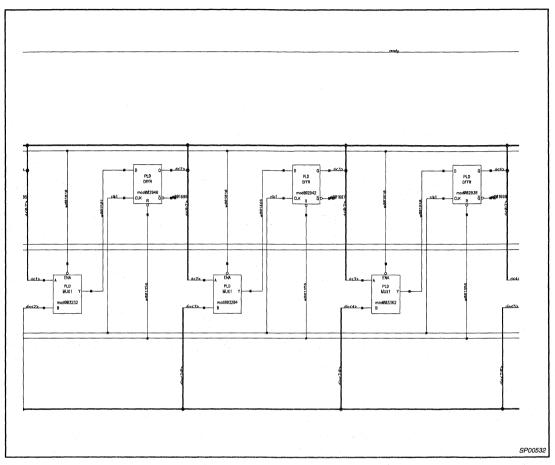

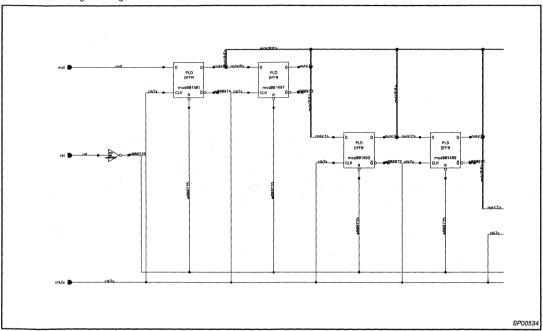

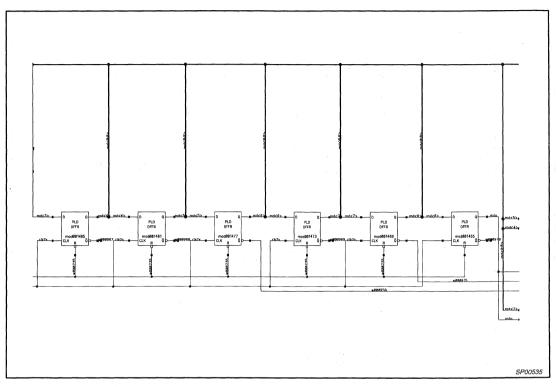

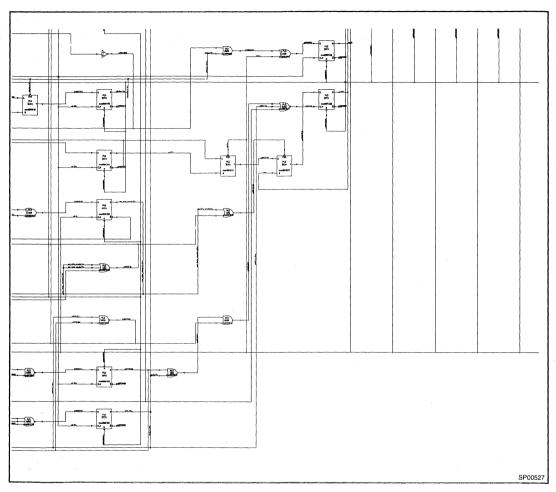

Figure 1 gives a high level block diagram of the XPLA™ architecture. The XPLA™ architecture consist of Logic Blocks which are interconnected by a Zero-power Interconnect Array (ZIA). The ZIA is a virtual crosspoint switch. Each Logic Block is essentially a 36V16 device with 36 inputs from the ZIA and 16 macrocells. Each Logic Block also provides 32 ZIA feedback paths from the macrocells and I/O pins. The number of Logic Blocks contained within a device determines the macrocell count of the device. For example, devices containing 2, 4, and 8 Logic Blocks are 32, 64, and 128 macrocell devices, respectively.

From this point of view, this architecture looks like many other CPLD architectures. What makes the CoolRunner™ family unique is what's inside each Logic Block and the design technique used to implement these Logic Blocks. The contents of the Logic Block will be described next.

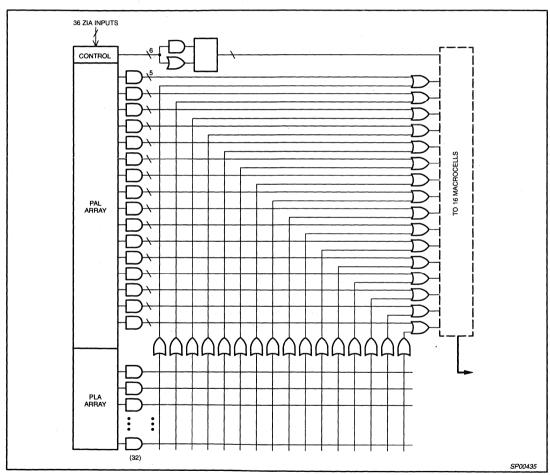

# Logic Block Architecture

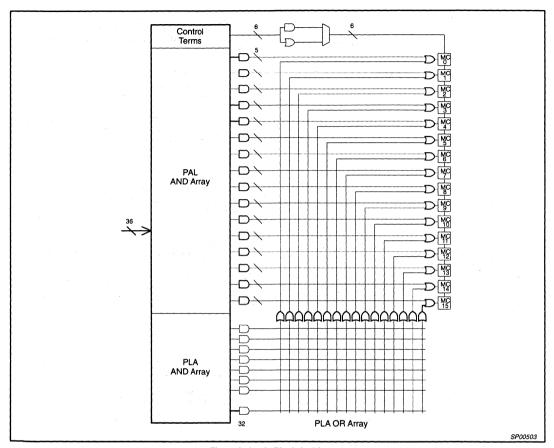

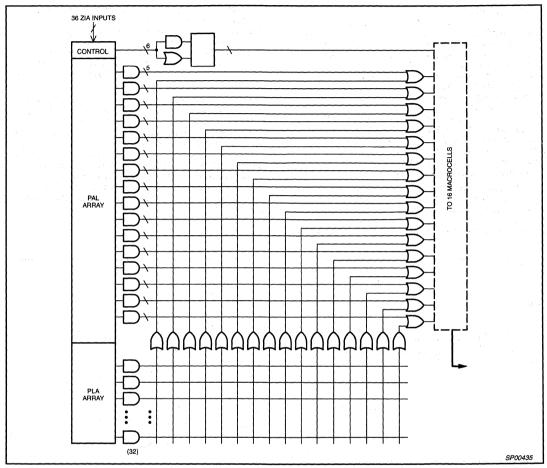

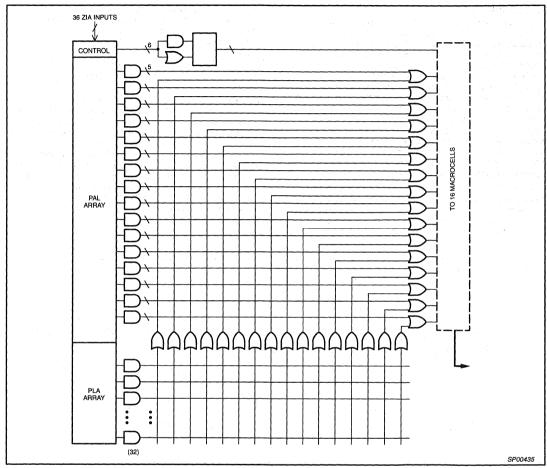

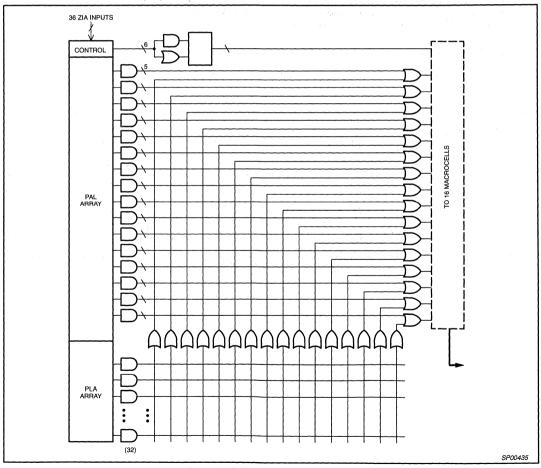

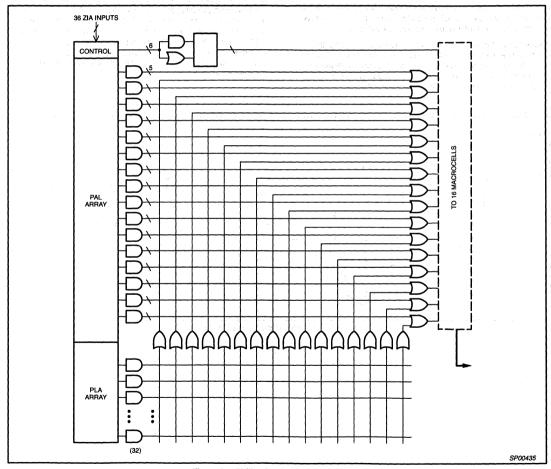

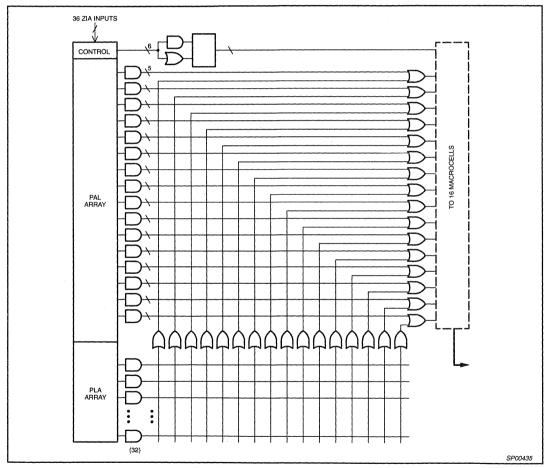

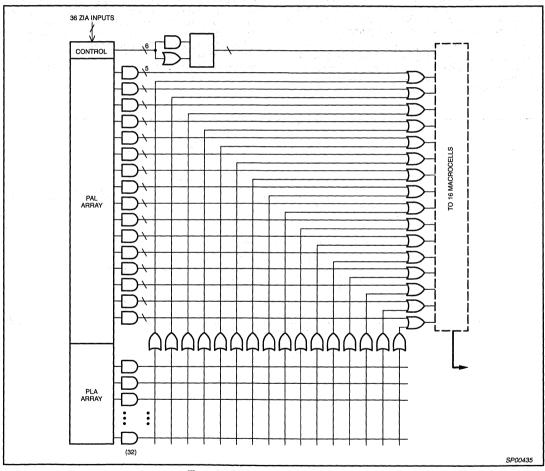

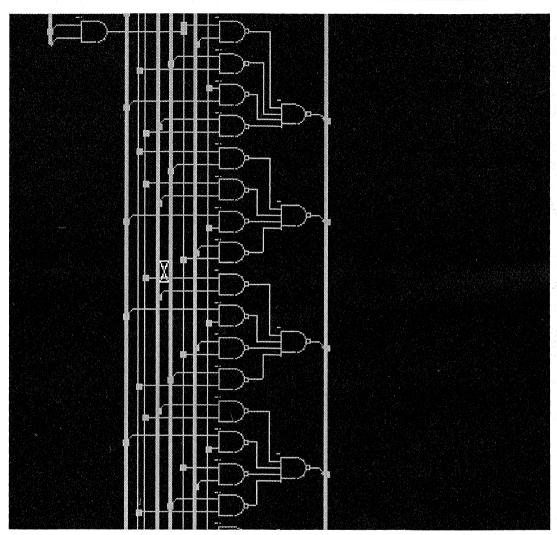

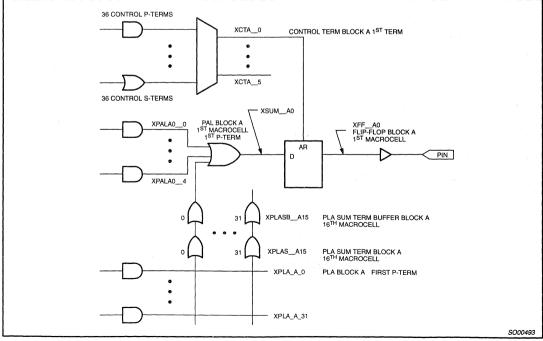

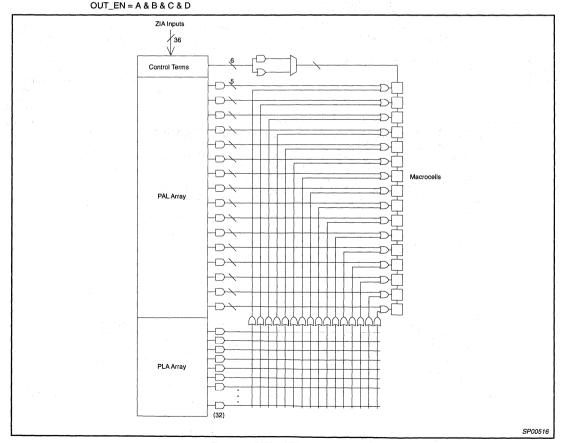

Figure 2 illustrates the Logic Block Architecture. Each Logic Block contains Control Terms, a PAL Array, a PLA Array, and 16 macrocells. The 6 Control Terms can individually be configured as either AND or SUM product terms and are used to control the preset/reset and output enables of the 16 macrocell's flip-flops. The PAL Array consists of a programmable AND array with a fixed OR array while the PLA array consist of a programmable AND array with a programmable OR array. The PAL array provides a high speed path through the array while the PLA array provides increased product term density.

Each macrocell has 5 dedicated product terms from the PAL array. If a macrocell needs more than 5 product terms, it simply gets the

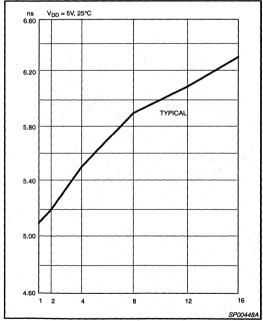

additional product terms from the PLA array. The PLA array consists of 32 product terms which are available for use by all 16 macrocells. For the 5V PZ5032 the additional propagation delay incurred by a macrocell using 1 or all 32 PLA product terms is just 2ns. So the total pin-to-pin tp\_D for the PZ5032 using 6 to 37 product terms is 8ns (6ns for the PAL + 2ns for the PLA).

The XPLA™ architecture is very accommodating for implementing last minute design changes. In fact, 16 million worst case designs (designs which used all of the I/O Pins and all of the Macrocells) were implemented in the PZ5032 with fixed pins & macrocells and all but 30 designs were able to route. Therefore 99.998% of these worst case designs were able to route with the pins fixed after the design was changed.

The reason why the XPLA™ architecture accommodates last minute design changes is because the PAL product terms are dedicated to a given macrocell and in addition there is a free pool of 32 PLA product terms which can be used by any of the 16 macrocells. If a macrocell uses less than 5 product terms and the design change requires a total of 5 product terms, the design is guaranteed to fit because the 5 PAL product terms are dedicated to each macrocell. There is no borrowing between macrocells. Borrowing is a nice feature until the macrocell whose product terms were borrowed wants its product terms back because of a last minute design change. If a design change requires more than 5 product terms, unused PLA product terms are used by the macrocell. In an average design, less than 20 PLA product terms are used so there are typically 12 PLA product terms available to implement last minute design changes.

Figure 1. XPLA™ Block Diagram

Figure 2. Logic Block Architecture

1997 Apr 10 22

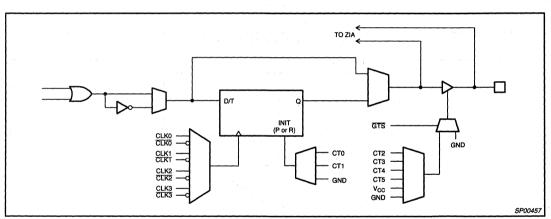

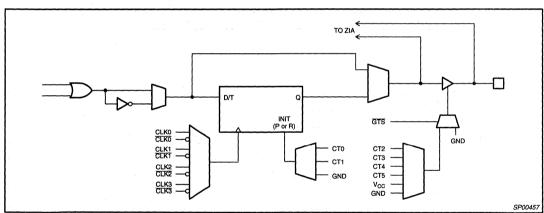

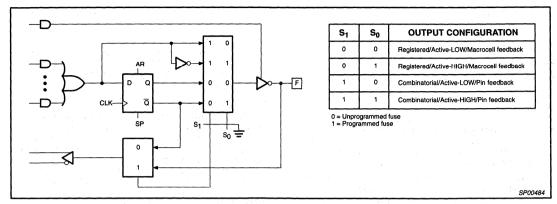

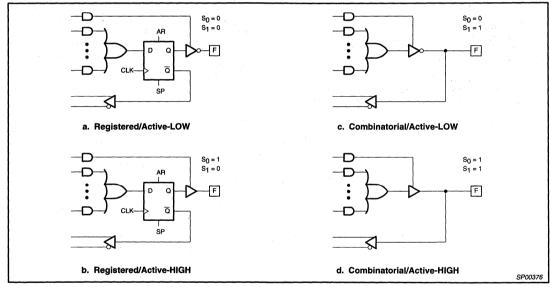

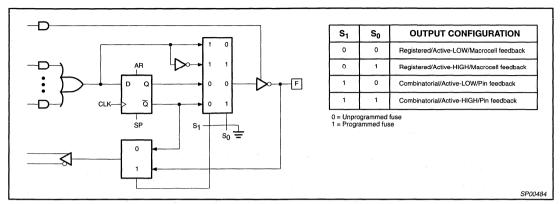

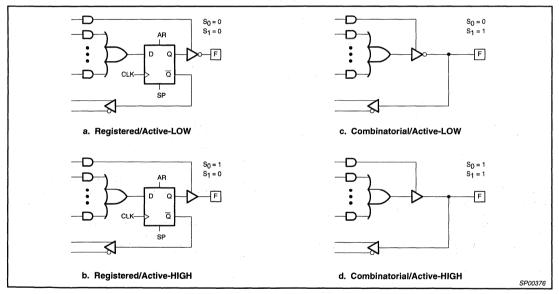

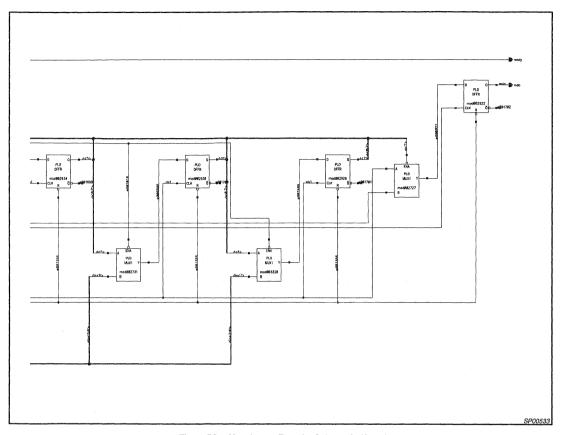

## **Macrocell Configuration**

equation).

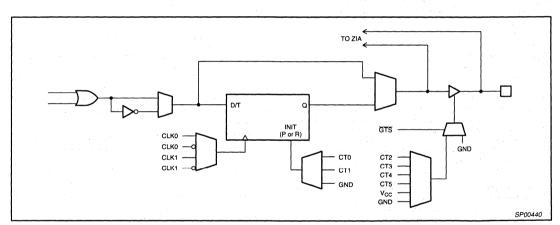

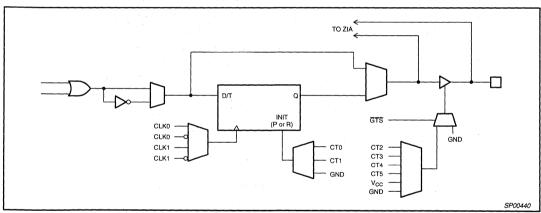

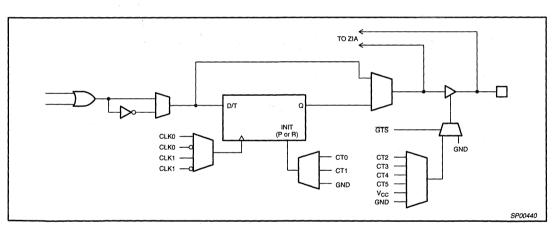

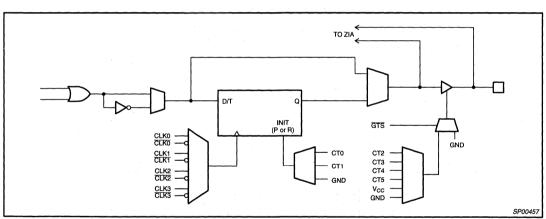

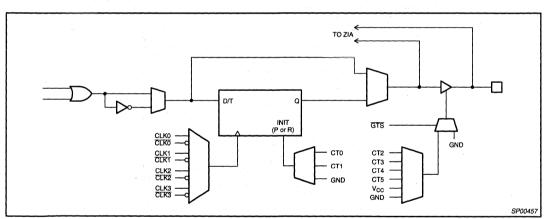

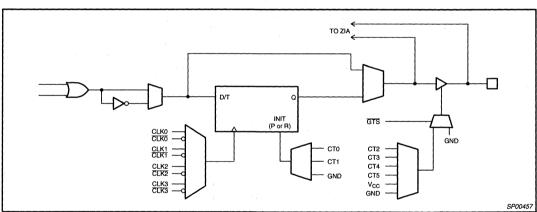

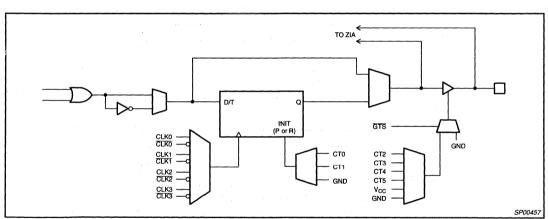

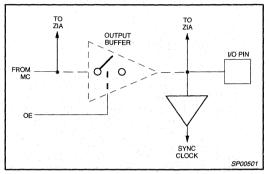

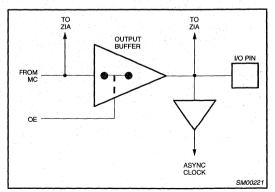

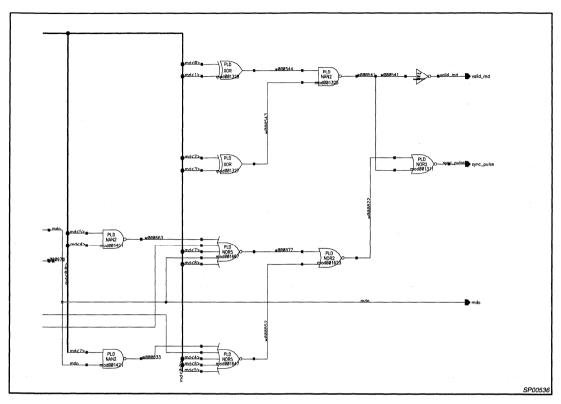

Figure 3 shows the architecture of the macrocell used in the CoolRunner™ family. The macrocell consists of a flip-flop which can be configured as either a D or T type. A D-Type flip-flop is generally more useful for implementing state machines and data buffering. A T-Type flip-flop is generally more useful in implementing counters. All CoolRunner™ family members provide both synchronous and asynchronous clocking and provide the ability to clock off either the falling or rising edges of these clocks. These devices are designed such that the skew between the rising and falling edges of a clock are minimized for clocking integrity. There are 2 clocks (CLK0 and CLK1) available on the PZ3032/PZ5032 devices and 4 clocks (CLK0 through CLK3) available in the PZ3064/PZ5064 and PZ3128/PZ5128 devices. Clock 0 (CLK0) in each of these devices is designated as the "synchronous" clock and must be driven by an external source. Clocks 1, 2, and 3 (CLK1, CLK2, and CLK3) can either be used as a synchronous clock (driven by an external

Two of the control terms (CT0 and CT1) are used to control the Preset/Reset of the macrocell's flip-flop. The Preset/Reset feature

source) or as an asynchronous clock (driven by a macrocell

for each macrocell can also be disabled. The other 4 control terms (CT2-CT5) can be used to control the Output Enable of the macrocell's Output Buffers. The reason why there are so many control terms dedicated for the output enable of the macrocell is to insure that all CoolRunner™ devices are PCI compliant. The macrocell's output buffers can also be always enabled or disabled. All CoolRunner™ devices also provide a Global Three-State (GTS\*) pin which, when pulled low, will three-state all the outputs of the device. This pin is provided to support "In-Circuit Testing" or "Bed-of Nails Testing".

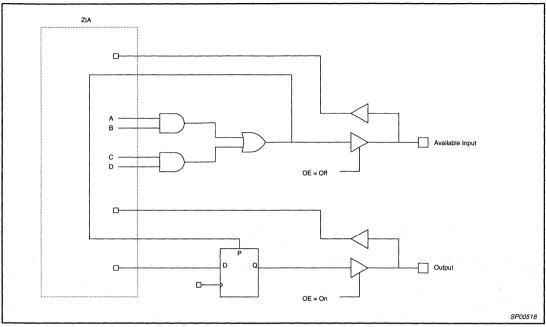

There are two feedback paths to the ZIA; one from the macrocell and one from the I/O pin. The ZIA feedback path before the output buffer is the macrocell feedback path while the ZIA feedback path after the output buffer is the I/O pin ZIA path. When the macrocell is used as an output, the output buffer is enabled and the macrocell feedback path can be used to feedback the logic implemented in the macrocell. When the I/O pin is used as an input, the output buffer will be three-stated and the input signal will be fed into the ZIA via the I/O feedback path and the logic implemented in the buried macrocell can be fed back to the ZIA via the macrocell feedback path.

Figure 3. Macrocell Architecture

1997 Apr 10 23

# How to use the programmable, Global 3-State feature on CoolRunner™ devices

All CoolRunner™ devices include a Global 3-State (GTS) feature which supports "In-Circuit-Testing" or "Bed-of-Nails-Testing". The GTS feature is made available via a Global Tri-State pin (GTS\*) which, when driven to a Low logic level, will 3-State all the outputs of the device. The GTS feature is optionally invoked as part of the user's design, and is provided through a dedicated pin on each CoolRunner™ device (please refer to the individual device data sheets). The default condition is that the GTS feature is not invoked, and that the related pin is instead available as a dedicated input pin (designated IN2 on all CoolRunner™ device packages).

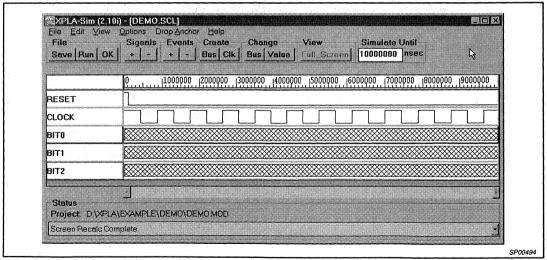

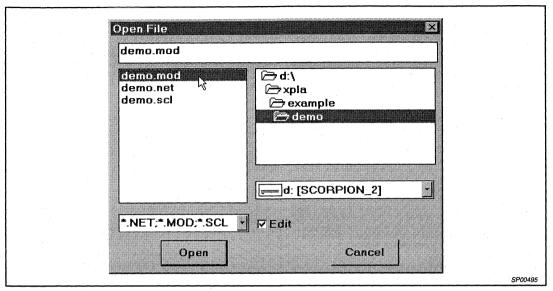

The GTS feature is invoked by setting the device under test property in the user's design file. In the XPLA Designer software environment, this is achieved by including the following property statement in the header section of the design:

XPLA Property 'dut on';

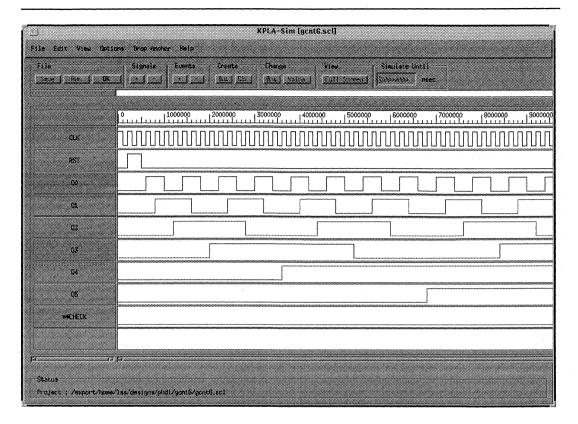

When this property is set, the GTS feature can also be simulated in the XPLA Designer environment. After including the 'dut on' property in the design, the RESERVED\_DUT signal automatically appears in the simulator signal list the first time a .SCL (Simulation Control Language) is created. If a new or subsequent .SCL file is created, the user must add a new signal and select RESERVED\_DUT as its name to enable simulation of this feature. In either case, the RESERVED\_DUT signal may be driven in the simulation by any waveform, similar to any other input. The difference, of course, is that all outputs are 3-stated whenever the RESERVED\_DUT signal is driven to a Low logic level.

# How to use synchronous and asynchronous clocks in CoolRunner™ devices

All CoolRunner™ devices provide multiple clock inputs, and support both synchronous and asynchronous clocking of the devices' internal registers. Clock inputs are associated with dedicated pins on CoolRunner™ device packages (please refer to the individual device data sheets), and the number of available clocks depends upon device density.

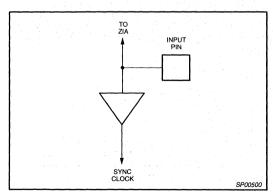

The clock inputs also have well-defined capabilities, depending upon whether their associated pin is a dedicated input or a general purpose I/O. CLK0 on any CoolRunner™ device is always associated with a dedicated input which, when used as a clock input, always serves as a synchronous clock driven solely by an externally-provided signal.

All other clocks (e.g., CLK1, CLK2, CLK3) are associated with a general purpose I/O pin and may be used to implement either synchronous or asynchronous (i.e., complex, or term-based) clocks. When used as a clock signal driven solely by an externally-provided input, these clocks perform similar to CLK0. Since these clocks are associated with a general purpose I/O, this isolates the related macrocell, although the macrocell's feedback path is still available, thus enabling use of the macrocell as a "buried" node or logic path.

When using CLK1, CLK2, or CLK3 to implement asynchronous clocks, there are some special considerations. In this case any or all I/O pins and feedback paths may be used to form the asynchronous clock. However, the clock must ultimately be driven by a macrocell associated with one of the general purpose I/O pins specified for clocking per the device data sheet. Because a specific macrocell ultimately drives the asynchronous clock, the associated general purpose I/O pin is no longer available for use (except as an external monitoring or distribution point for the asynchronous clock). Also, performance for asynchronous clocking is variable depending on the

specific application and must be determined through simulation or analysis by the user. This is because the levels of logic complexity and number of feedback paths incurred in forming the asynchronous clock determine the delay in the clock path.

Please note that all of the clock signals in a CoolRunner™ device are available to all of the macrocells in that device. A multiplexer is associated with each macrocell for the purpose of providing any of the available clock signals to the macrocell's register element. Furthermore, clock polarity can be selected for each macrocell, thus allowing any macrocell's register element to be clocked from either the rising or falling edge of any clock signal in the device.

# How to use Output Enables in CoolRunner™ devices

All CoolRunner™ devices provide the ability to control each general purpose I/O pin through the use of an output enable (OE) signal. OE signals allow for the 3-stating of an output pin in bus applications, and also allow for the implementation of bi-directional pins in the CoolRunner™ devices. Within each logic block (i.e., group of 16 macrocells), four control signals are provided to support OE generation. Because these control signals are provided at the logic block level, each logic block can independently generate OE control for its associated outputs.

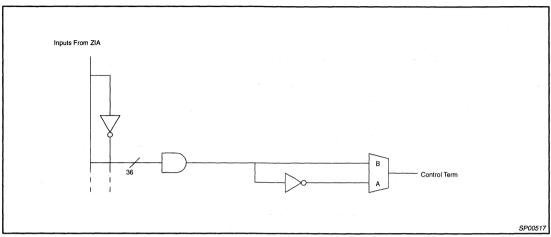

Each of these four control signals are provided to the input of a multiplexer that is associated with each output buffer control, thus allowing each general purpose I/O pin in the logic block to have OE control based on one of these four control signals. Each of these four control signals may directly be either a sum term or product term of any or all of the 36 inputs into the logic (the 36 inputs into the logic block may be driven directly by external signals and/or by feedback paths from logic generated in the device). However, these four control signals cannot directly be a sum of products. For example:

A # B # C # D # .... is a sum term, which is directly supported

A & B & C & D & .... is a product term, which is directly supported

(A&B) # (C&D) # .... is a sum of products term, which is NOT directly supported

Complex OE signals that are based on a sum of products term must use a 'buried' node that is not collapsed during the design compilation. The 'buried' node is driven by the sum of products equation, and the OE signal is assigned to be driven by the node.

# How to use Presets and Resets in CoolRunner™ devices

All CoolRunner™ devices support asynchronous Preset/Reset control for the register elements associated with each macrocell. Within each logic block, two control signals are provided for Preset/Reset control. Like OE signals (described above), the Preset/Reset control signals may be a sum term or a product term of any/all of the inputs into the logic block.

Each of the two control signals drive multiplexers that are associated with each register element. The multiplexer, in turn, controls either a Preset or Reset function defined for the register. Please note that the user must select between asynchronous Preset and asynchronous Reset functionality for a register element; it is not possible to implement both asynchronous Preset and asynchronous Reset for the same register.

Synchronous Preset/Reset may be synthesized for each register element. This is achieved by 'gating' the logic input to a register element with an appropriate control signal, as specified in the logic

design. In the XPLA Designer environment synchronous preset and reset dot extensions are available to automatically synthesize the required structures. For synchronous preset the .CLR or .SR extension can be utilized and for synchronous reset the .SET or .SP extensions may be used.

# How to implement Clock Enable signals in CoolRunner™ devices

Clock Enable (CE) signals are indirectly supported in CoolRunner™ devices through synthesis. To implement a CE signal, an appropriate control is 'gated' with both the logic generated to drive the register element and the register's output feedback. In the XPLA Designer software environment, a .CE extension is provided for specifying a CE signal in the design and synthesis is automatic, such that it is not necessary to explicitly specify the 'qatino'.

In other environments, it may be necessary to explicity implement the CE functionality. For a register element driven by the logic signal DAT\_IN to produce the output signal DAT\_OUT, the CE signal CLKEN is used in the definition of DAT\_OUT as follows to implement the clock enable functionality:

DAT\_OUT := (DAT\_IN & CLKEN) # (!CLKEN & DAT\_OUT.q)

where ':=' indicates that DAT\_OUT is a registered signal, the '.q' extension indicates the feedback path from the register, and the signal CLKEN is a clock enable signal driven by external signals, internally-generated logic, or both.

# How to determine output states upon power up in CoolRunner™ devices

When a CoolRunner™ device is powered-up, all output buffers are disabled, so that all outputs are 3-stated. The delay from valid V<sub>DD</sub> to valid reset is specified in all CoolRunner™ datasheets as t<sub>INIT</sub> with a maximum delay of 50 microseconds (μs). After t<sub>INIT</sub>, all registered outputs are reset to a low logic level, and all combinatorial outputs are resolved to the appropriate state as determined by the inputs and/or internally-generated logic from which they are formed. However, please note that only a maximum delay is specified for t<sub>INIT</sub> and no minimum delay is guaranteed. If external input signals are still at undeterminable (e.g., 3-state) logic states after the CoolRunner™ device has transitioned through its power-up reset sequence, dependent combinatorial outputs will be unknown.

# **PLA Product Term Sharing**

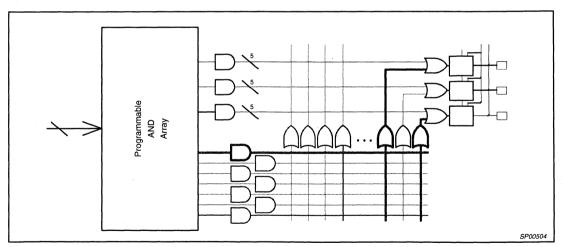

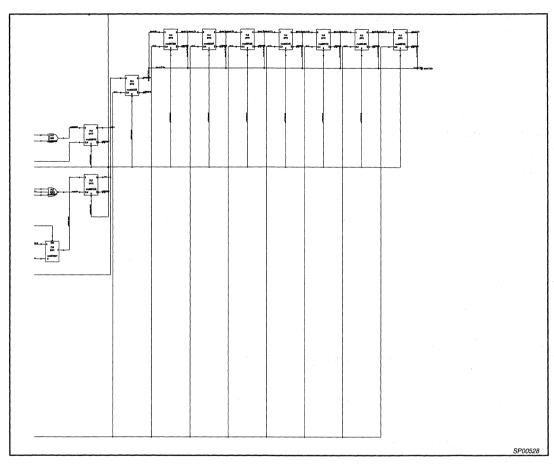

Another feature offered by the XPLA™ architecture, which cannot be offered by other competing architectures, is product term sharing. In address decode circuits, some state machines, and other types of designs there are product terms which are common to a number of macrocells. The XPLA™ architecture allows sharing of PLA product terms between macrocells as shown in Figure 4. In this example, it shows one PLA product term being shared by two macrocells. In this case, there is "effectively" 33 PLA product terms because one of them is shared between two macrocells. PLA product term sharing increases the "effective" density of the device and allows larger designs to fit in the same macrocell count device. If needed, all 16 macrocells could share all 32 PLA product terms.

Figure 4.

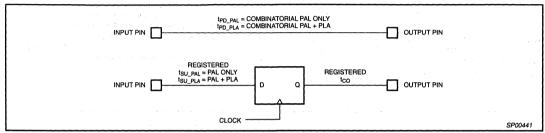

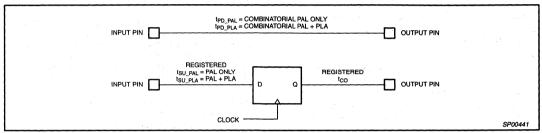

# **Simple Timing Model**

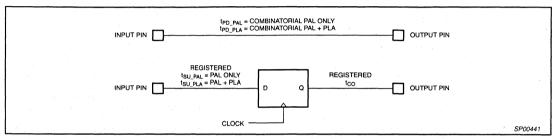

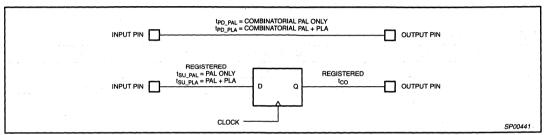

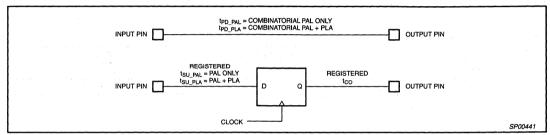

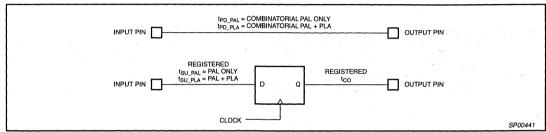

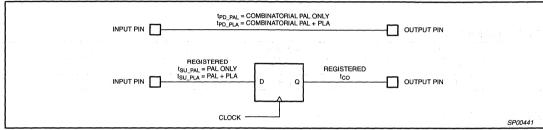

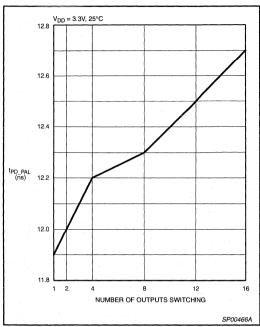

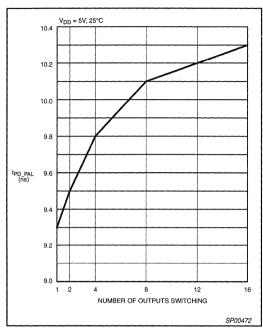

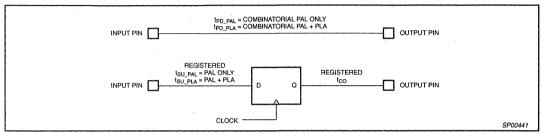

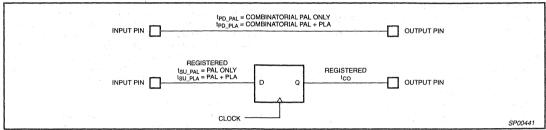

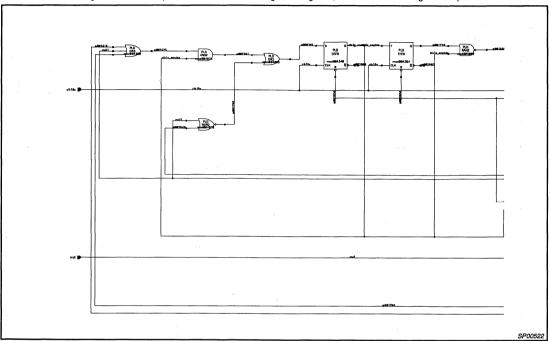

Figure 5 shows the CoolRunner™ Timing Model. As one can see from this illustration, the CoolRunner™ timing model looks very much like a 22V10 timing model in that there are three main timing parameters including tpD, tsU, and tcO. In other competing architectures, the user may be able to fit the design into the CPLD but is not sure whether system timing requirements can be met until after the design has been fit into the device. This is because the timing models of competing architectures are very complex and include such things as: timing dependencies on the number of parallel expanders borrowed, sharable expanders, varying number

of X and Y routing channels used, etc. In the XPLATM architecture, the user knows up front whether the design will meet system timing requirements. This is due to the simplicity of the timing model. For example, in the PZ5032 device, the user knows up front that if a given output uses 5 product terms or less, the  $t_{\text{PD}}$  = 6ns, the  $t_{\text{SU}}$  = 4ns, and the  $t_{\text{CO}}$  = 5.5ns. If an output is using 6 to 37 product terms, an additional 2ns is added to the  $t_{\text{PD}}$  and  $t_{\text{SU}}$  timing parameters to account for the time to propagate through the PLA array—this is the only variation in timing that exists when using the XPLATM architecture!

Figure 5. CoolRunner™ Timing Model

# Fast Zero Power (FZP™)

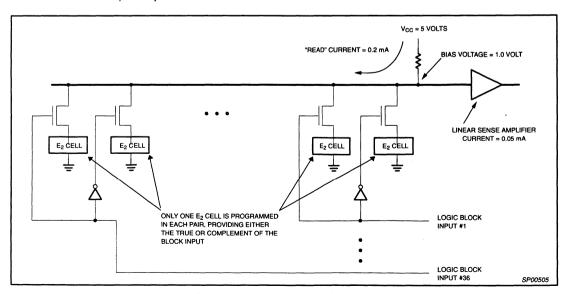

In CPLD architectures, the methods implemented to propagate logic-level transitions in the product term array are derived from the original bipolar simple PLD devices. Within a CPLD, each product term in the array is "fed" by all of the inputs into the logic block (see Figure 1). The number of inputs to the logic block vary by CPLD supplier, but are generally 1.5-to-2.5 times the number of macrocells in the logic block. The most commonly implemented logic block size in existing CPLDs is the 36V16, meaning that there are 36 inputs into a logic block with 16 macrocells. Since all CPLD architectures make both true and complement forms of the logic block inputs accessible to the product terms, the number of capacitive loads on the product term "word line" becomes significant and can be modeled with an equivalent total capacitance of 2 of.

Logic block inputs (and their complement) are connected to the product term "word line" via pass gates and the "word line" is biased with a "read" current of roughly 0.2 mA that can be modeled as the source voltage through a resistor. The time required to propagate a logic-level transition on the "word line" becomes a function of the 2 pf total capacitance of all the pass gates, the "read" current supplied for biasing the "word line", and the voltage differential that defines a logic-level transition.

Existing CPLDs implement sense amplifiers at the end of each "word line" to achieve fast propagation delays. These sense amplifiers operate in the linear region, and ensure fast propagation times by amplifying a 100 mV increase to the 1 Volt bias voltage on the "word line" such that it represents a full CMOS voltage swing. Using the equation I = C(dv/dt), the time required to increase the "word line" voltage can be calculated as follows:

$$dt = (C dv)/I = (2 pf) * (0.1 v) / 0.2 mA = 1 ns.$$

The sense amplifier itself contributes another 1 ns to the delay, and requires a current of about 0.05 mA. Because this is only a portion of the CPLD's total propagation delay (tpp), it becomes necessary to reduce the "word line" delay to ensure high-performance for the CPLD. This is achieved by increasing the "read" current, as indicated in the calculations previously discussed.

The benefits of the sense amplifier are clear—a full voltage swing can be realized in a very short time by supplying the maximum current that the sense amplifier accommodates. In lower-density CPLDs (i.e., less than 128 macrocells), this maximum current is usually not prohibitive from a thermal dissipation and a supply voltage standpoint. As an alternative, consider what would happen if the sense amplifier was not used and it became necessary to increase the voltage by 4 volts to realize a full CMOS swing from the 1 volt bias. With a 0.2 mA "read" current, the time required to realize a 4 volt increase is calculated as follows:

$$dt = (2 pf) * (4.0 v) / 0.2 mA = 40 ns.$$

To get back to the 1 ns performance of the sense amplifier, the "read" current would have to be increased to 8 mA for each product term. This would translate to a standby current of more than 5 amps for a device with 5 product terms per macrocell, 16 macrocells per logic block, and 8 logic blocks per device (i.e., a common 128 macrocell CPLD).

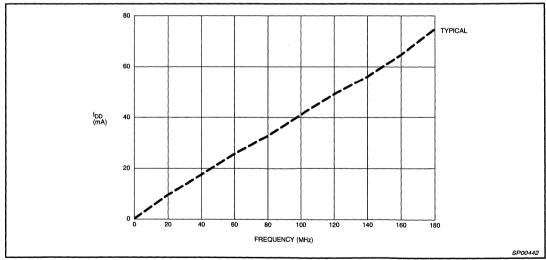

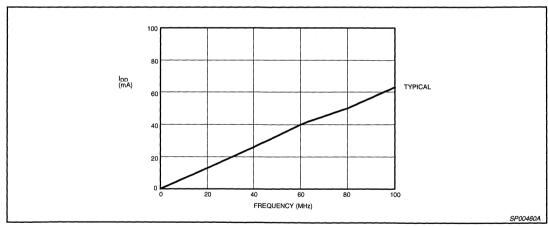

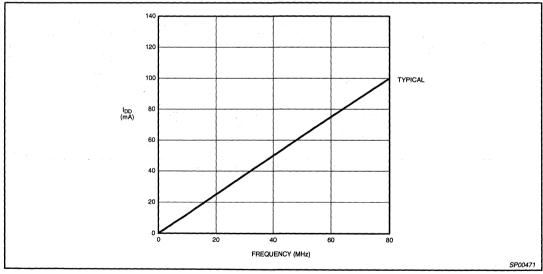

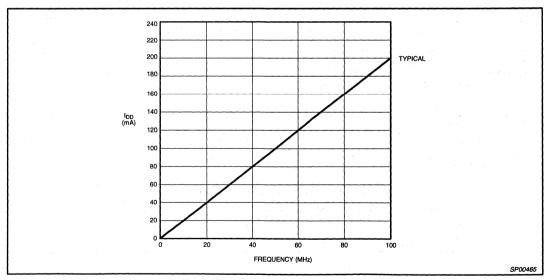

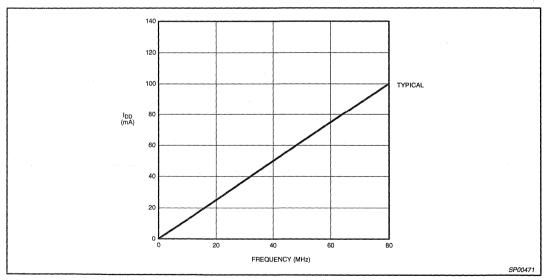

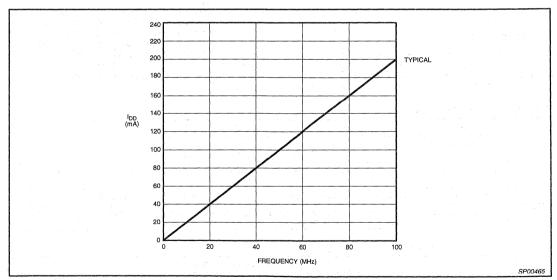

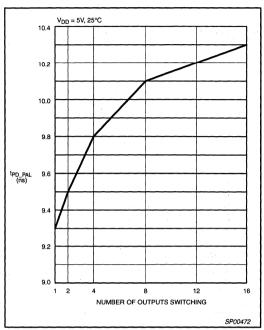

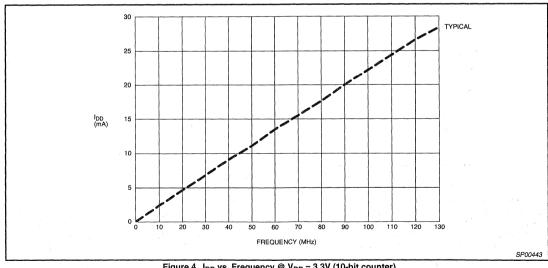

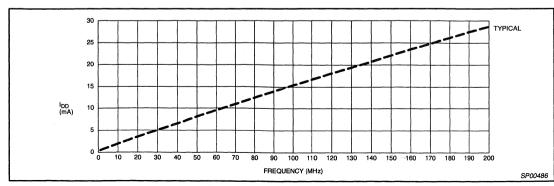

The benefits of the sense amplifier are not free, though. As discussed above, each product term requires a standby current of 0.25 mA. This translates into a total standby current of 160 mA for the common 128 macrocell CPLD. To operate a 16-bit counter in every logic block at f<sub>cnt</sub> = 50 MHz., the current requirement for this device increases to about 240 mA. Even though these currents are a vast improvement over not using a sense amplifier, they are still considerably high for today's digital designs-especially when the end-product is portable or battery-powered. When it is necessary to reduce power in these devices, the "read" current must be limited. This is achieved during device programming by setting the device to low-power, or "non-turbo" mode. However, as indicated in the equations above, reducing the "read" current causes an increase in the time it takes to propagate the logic-level transition through the product term. The end result is a significant decrease in the overall performance of the CPLD.

Figure 1. Product Term in Existing CPLDs

# Fast Zero Power (FZP™)

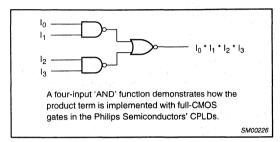

The Philips FZP™ design technique takes a new and innovative approach to implementing the product term array.

Instead of employing a bipolar design technique (i.e., sense amplifiers), Philips instead becomes the first CPLD supplier to take a true CMOS design approach. The result is the first TotalCMOS<sup>TM</sup> CPLD; i.e., a CPLD that is CMOS both in process technology and design technique. In the FZP<sup>TM</sup> design technique, represented in Figure 2, the product term array is implemented by cascading the logic in a tree of full-CMOS gates. These full-CMOS gates switch in 200 picoseconds (ps), and are cascaded in a way that achieves speed performance comparable to the sense amplifier approach in existing CPLDs.

Figure 2. Representation of a Product Term using the Philips FZP™ Design Technique

Cascading the gates distributes the capacitance associated with the true and complement logic block inputs, so that this capacitance is no longer lumped on a single node. Furthermore, the switching

current behaves in a manner similar to that of random logic in a gate array. The static current for each gate is incredibly small—about 1 pico-amp (pA). The total instantaneous dynamic current is also small, since only the gates in one path of the tree switch, and these gates switch in succession rather than all at the same time.

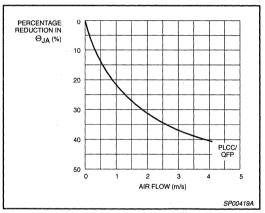

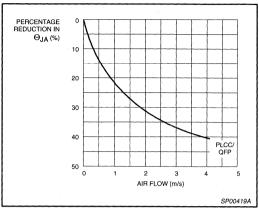

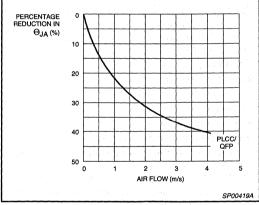

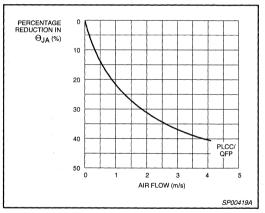

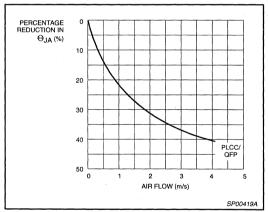

The advantages of FZP™ are numerous. Total standby current for these CPLDs is under 100 micro-amps—at least 1000 times less than that exhibited by CPLDs that use sense amplifiers. Dynamic power is also decreased relative to existing CPLDs—by as much as 70% for a device whose logic is fully-populated with 16-bit counters operating at 50 MHz. Best of all, these power savings are realized with no impact on performance and no externally-controlled provisions, such as power-down circuitry. Because power consumption is so low, TQFP packaging options can now be offered that were once considered impossible due to thermal limits. Also, CPLDs can now rival the gate densities that were previously attained only by FPGA's and ASIC's. As a result, FZP™ is an enabling technology for CPLDs since it makes their use possible in applications where their high-power-consumption and/or low-performance at low-power was previously prohibitive.

The disadvantages of FZP™ are trivial. It is possible to achieve slightly faster data paths by supplying high currents to sense amplifiers. This path is only a portion of the CPLDs total Tpd, though, such that the difference between a sense amplifier's speed performance and the speed of the CMOS gate chain becomes negligible. The CMOS gate chain also requires more die area in the core than sense amplifiers. In fact, this would likely preclude a full-CMOS gate approach in the older, two-layer metal processes used to manufacture most existing CPLDs. However, Phillips has overcome this obstacle by manufacturing their CPLDs on a leading-edge, 0.5 micron, triple-layer metal process technology.

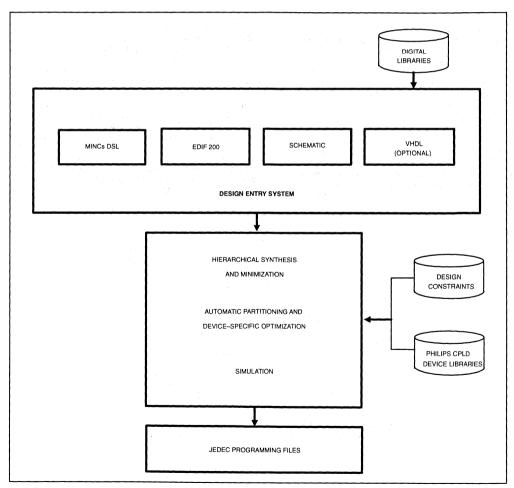

### **DEVELOPMENT SOFTWARE**

Philips software strategy is based on three elements:

- -Support for tools and design flows already in place at the customer site.

- Maintaining in-house expertise to facilitate optimum architecture and software interaction while adding valued utilities into the design process, and

- -To offer cost effective solutions that enable users easy access to Philips silicon technologies.

By supporting tools that designers already own, Philips hopes that costs for both licensing and maintenance can be maintained at reasonable levels, and that designer productivity can be enhanced as minimal learning is required.

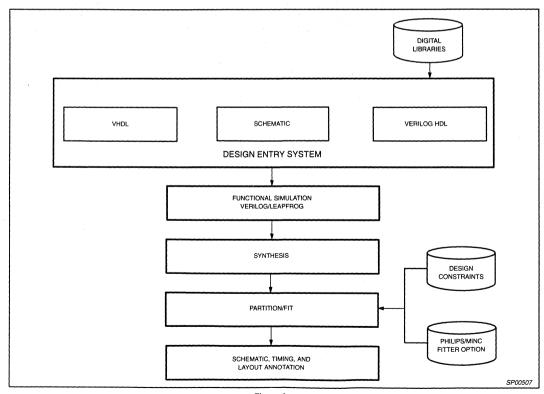

When considering the design process, it can be broken down into three elements: design creation, design verification, and design implementation. It is the Philips Semiconductors Programmable Product Group's belief that design creation tools are best handled by CAE companies whose charter it is to create the most useful software in completing this initial step. Philips supports the move to vendor independent design creation software and HDLs. Philips strategy involves focussing on design implementation software, so that design files can be efficiently and effectively implemented into Philips devices. In addition, Philips supports back annotation of delay information into software utilized for design verification.

The above strategy facilitates the need for partnerships, and Philips will continue to work with the CAE software industry to provide optimum, timely, and cost effective solutions. One example of a partnership is illustrated by Philips relationship with Minc Inc. to supply CPLD implementation software (i.e., fitters). As a result, Philips maintains redundant fitters for each device so that software support is always ensured for the design engineer.

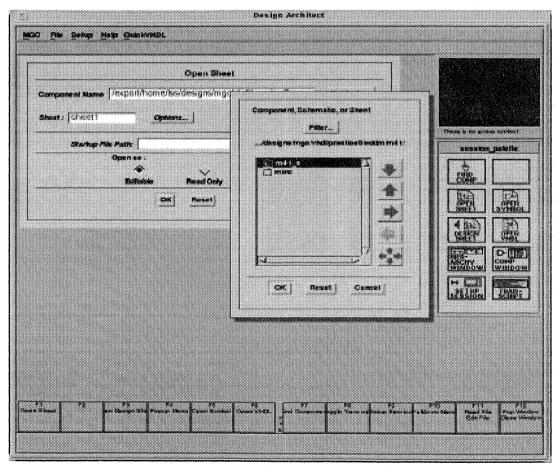

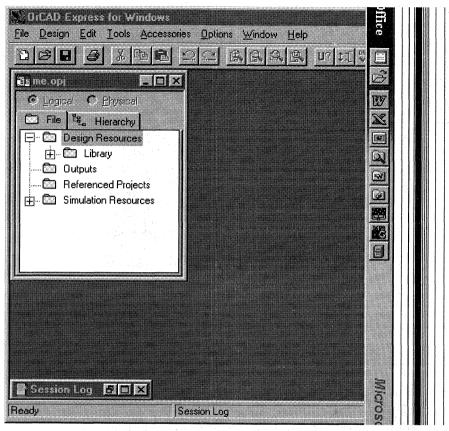

Philips' CPLD devices are currently supported in the following design environments: Cadence, Mentor, Viewlogic, Synario, Minc, Synopsys via Minc, and Philips' own XPLA™ Designer on personal computer and Unix workstations. Detailed descriptions follow that outline the design flows and software tools available in these environments.

# Philips/Cadence Design Environment

The Philips/MINC CPLD fitter is fully integrated into the Cadence PIC Designer™ software and the Cadence family of system design products. It is tightly integrated with both the Concept™ and Composer™ design entry systems, with Synergy™ VHDL and Verliog synthesis tools, and with Verliog-XL™ and Leapfrog™ VHDL simulation environments.

The Philips/Cadence design flow supports a top-down or mixed-level design methodology. Designs can be entered as schematics using Concept<sup>TM</sup> or Composer<sup>TM</sup>, or in an industry standard hardware description languages (HDLs) including VHDL and Verilog HDL. Maximum flexibility is provided through the ability to enter designs as a mixture of schematic-based and HDL-based design entry methods.

PIC Designer™ provides the ability to simulate the programmable logic design before device selection and partitioning, and again after the implementation of the design. PIC Designer™ performs an optimization of the user's programmable logic, and automatically generates Verilog models for the blocks associated with HDL descriptions. These models contain unit delays for functional simulation of the programmable logic early in the design process. This makes it easier to detect and correct errors, and helps users ensure that their logic will function properly in their overall system design.

PIC Designer™ performs architecture-specific partitioning and fitting based on user-defined design constraints, to ensure the best possible design implementation. This includes automatic implementation of the design, with a resulting list of single or multiple device alternatives which meet the design constraints. After device fitting, PIC Designer™ automatically redraws fully annotated schematics. Designs can be re-simulated with final timing using Verilog or Leapfrog™ VHDL for a detailed analysis of system operation and performance.

### System and Software Requirements

Cadence/Minc Software

- PIC Designer™

- Philips/MINC Fitter Option for PIC Designer™

- Synergy™ HDL synthesis

- Verilog or Leapfrog™ simulator

### **Recommended Operating Systems**

PIC Designer™ has been tested with the following operating systems:

- Hewlett-Packard HP-UX 9.05

- Sun MicroSystems SunOS 4.1.4 (V4.1.3 compatible)

- Sun MicroSystems Solaris 2.4 (requires SunOS compatibility mode)

Figure 1.

1997 Apr 10 30

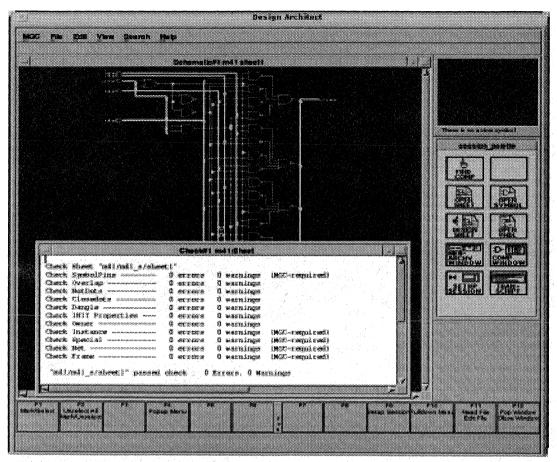

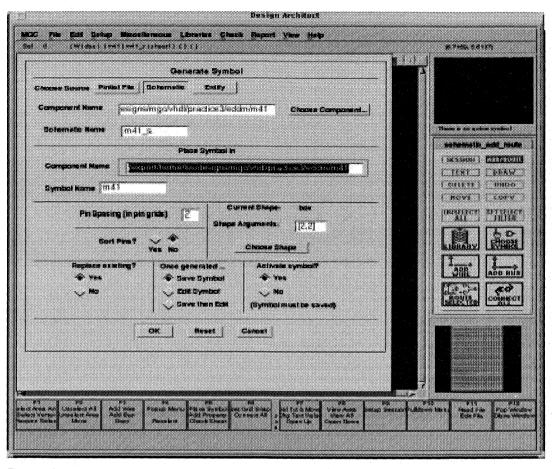

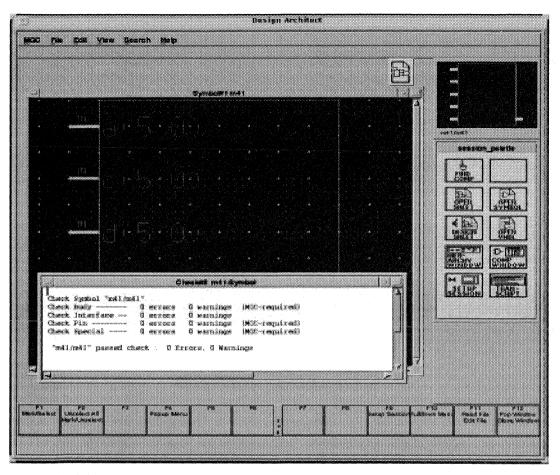

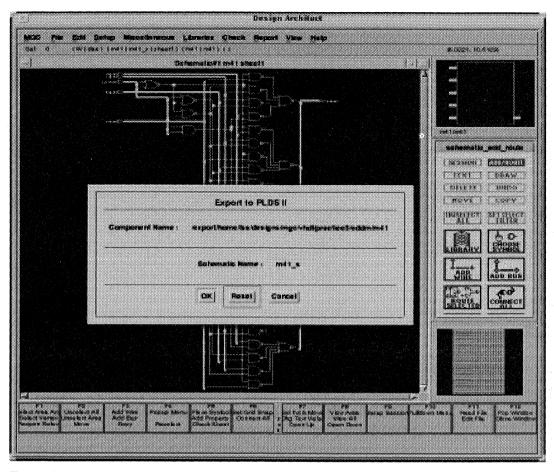

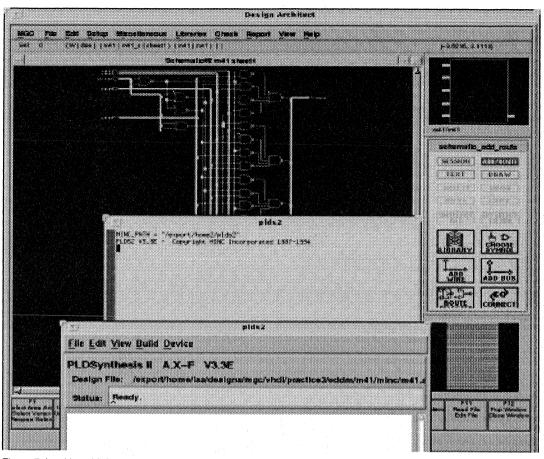

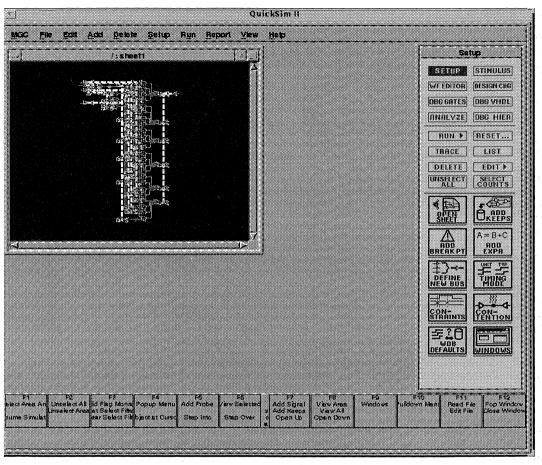

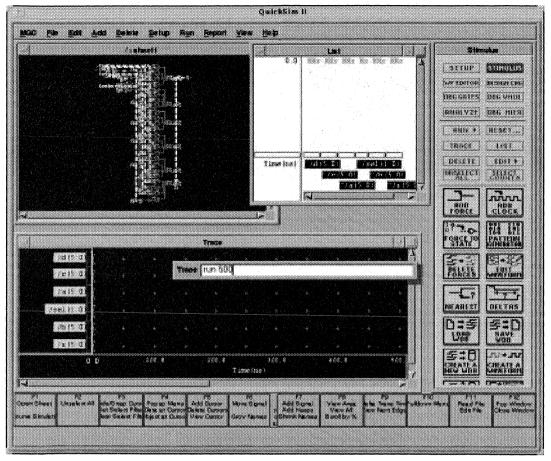

### Philips/Mentor Graphics Design Environment

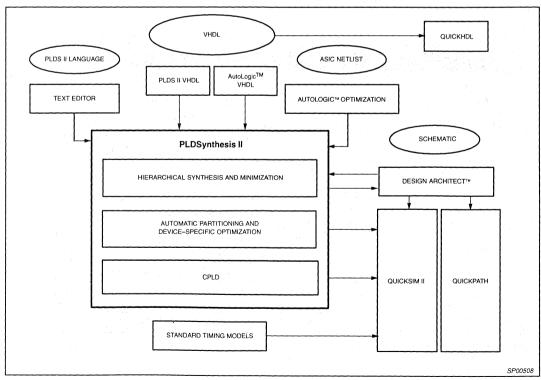

The Philips/MINC CPLD fitter is fully integrated into the Mentor Graphics PLDSynthesis II™ (PLDS II) software. PLDS II offers high-level design entry, device-specific optimization, automatic device selection, and patented multiple-device partitioning. It also leverages the design and simulation capabilities of Mentor Graphics Idea Station® to provide a total programmable design environment.

The Philips/Mentor Graphics design flow supports a top-down or mixed-level design methodology. A wide variety of design entry methods allows the designer to quickly complete their design. Designs can be entered as TTL or GENLIB schematics using Mentor Graphics Design Architect, as an ASIC netlist using AutoLogic™, or in hardware description language (HDL) form using either AutoLogic™ VHDL or PLDS II's own hierarchical design language (DSL™). Maximum flexibility is provided through the ability to enter designs as a mixture of the various design entry methods.

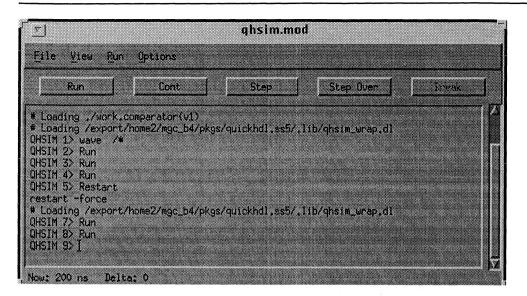

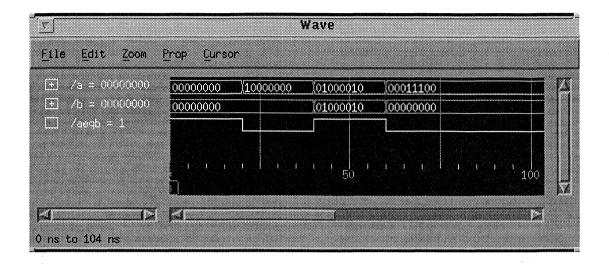

PLDS II automatically builds functional simulation models, and supports simulation before device selection and synthesis, including VHDL functional simulation using QuickHDL. PLDS II performs automatic device selection based on user-defined engineering constraints to ensure the best possible design implementation. It also automatically performs partitioning, fitting, and pin mapping. These features, coupled with fully hierarchical synthesis for any combination of CPLDs, improves both cost-efficiency and

time-to-market by facilitating fast and easy "What If" analysis for the design.

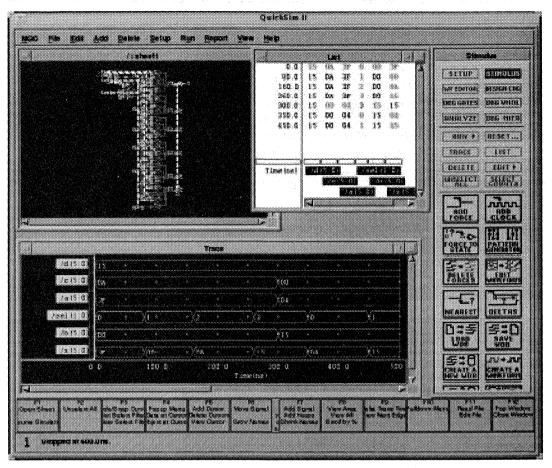

After device selection and synthesis, PLDS II generates JEDEC and Intel HEX files for programming the CPLD. It also automatically creates full documentation and physical schematics for the final implementation. These files are easily loaded into leading device models to assure convenient and accurate final simulation. Simulation support is available through Mentor Graphics QuickSim II using the Standard Timing Models that are included with PLDS II. The Standard Timing Models may also be used with Mentor Graphics QuickPath to perform static timing analysis.

### System and Software Requirements

Mentor Graphics Software

- Idea Station™

- PLDSynthesis II™ Version 3.6

- Philips/MINC Fitter Option for PLDSynthesis II™

### Recommended Operating Systems

PLDSynthesis II™ has been tested with the following operating systems:

- Hewlett-Packard HP-UX 9.05

- Sun MicroSystems SunOS 4.1.4 (V4.1.3 compatible)

- Sun MicroSystems Solaris 2.4 (requires SunOS compatibility mode)

Figure 2.

1997 Apr 10 31

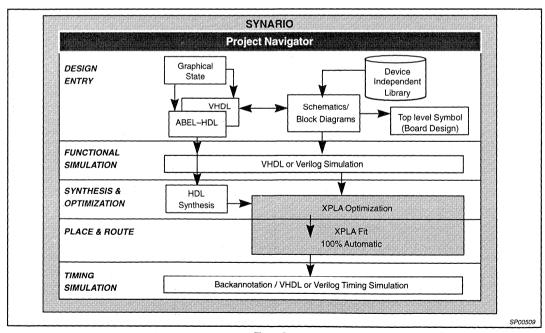

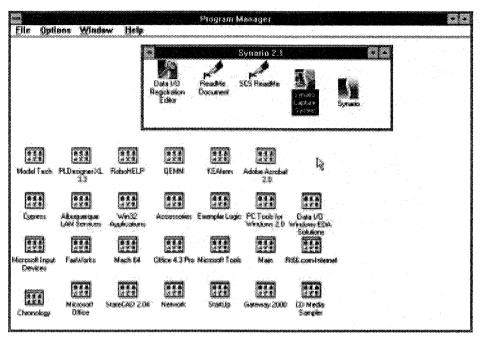

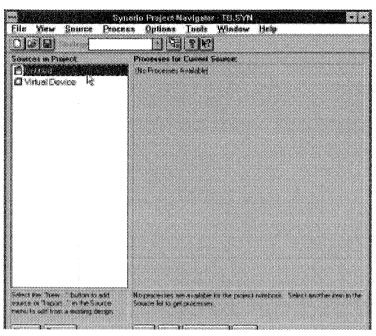

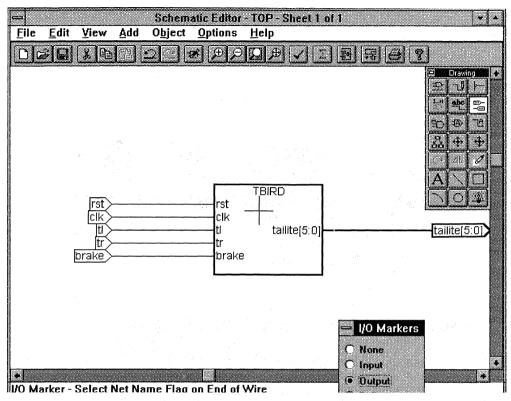

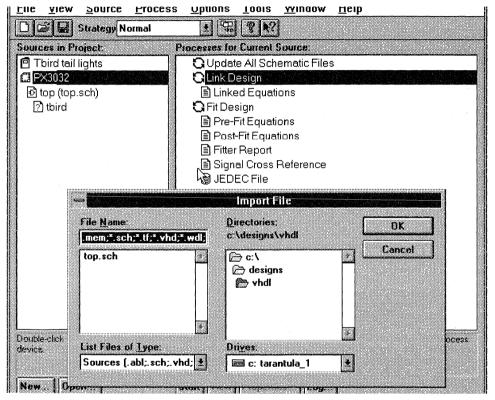

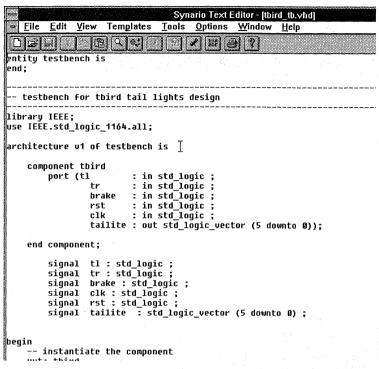

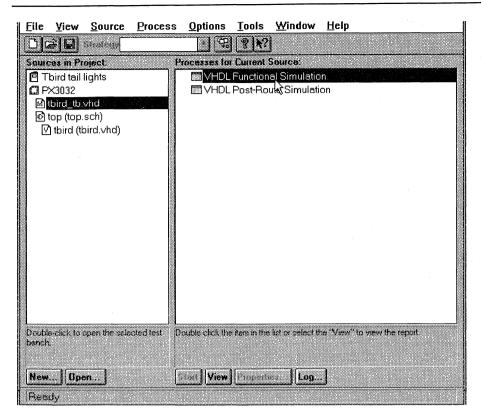

### Synario/Philips Design Environment

Synario offers a comprehensive suite of Windows-based tools for programmable logic design; incorporating best-of-class point tools that operate in a seamless design flow. The power behind Synario's integrated design system can be attributed to its Project Navigator. Its built-in knowledge of device architectures is leveraged each time a designer changes architectures, with an automatic reconfiguration of the design flow. After the designer selects a device, the Project Navigator presents the steps required to design, simulate, synthesize, and place-and-route the design. Synario users can move from entry to implementation in minutes, even when targeting an unfamiliar device architecture.

The value of Project Navigator increases for those designers transitioning to top-down design methodologies. HDLs, such as VHDL and Verilog, are well suited to handling the increasing complexity of CPLD and FPGA devices. The Project Navigator decreases the learning curve this transition creates, by supporting designers through each step in a pure HDL or mixed HDL-schematic based design process.

To support traditional or top-down design methods, Synario provides unsurpassed mixed-entry support along with functional and timing simulation options for both Verilog and VHDL users. Synthesis capabilities that interface to device-specific optimization and technology mapping are also available.

Synario is serious about good device support. Synario Device Kits include: schematic symbols; simulation models; logic synthesis and

device-fitting technology; place-and-route software; device specific examples and on-line help. Designers can be assured, Synario Device Kits provide vendor-qualified tools tailored specifically to a chosen architecture.

Synario-Philips Device Kit incorporates everything the designer needs for a CoolRunner™ XPLA design: schematic symbols; functional and timing simulation models; Philips Semiconductors' XPLA Optimization and Fitting software; and process management, design examples and on-line help for Philips device families. It serves as the interface from within Synario's Project Navigator, offering designers a highly integrated front-to-back design solution tailored for Philips CPLDs.

### System and Software Requirements

Synario Software:

- Synario Programmable IC Entry or Synario System Entry

- Synario VHDL, Verilog, or Verilog-Pro Simulators

- Synario ABEL, VHDL Synthesizers

### Philips Software:

- Synario Philips Device Kit (Syn-XPLA-PR)

### **Operation Systems supported**

- Windows 3.11, 95, NT 3.51or 4.0

Figure 3.

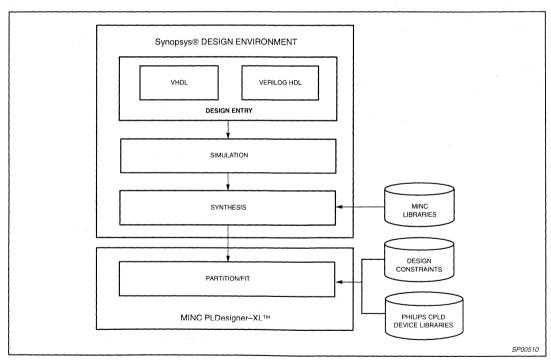

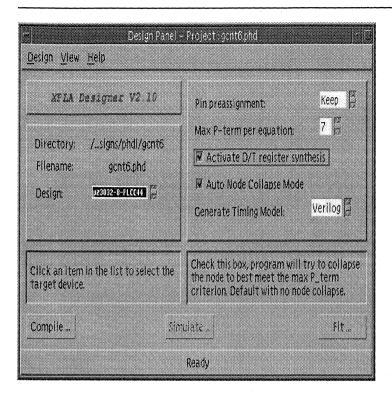

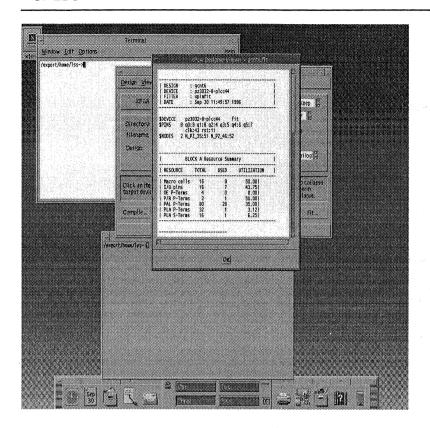

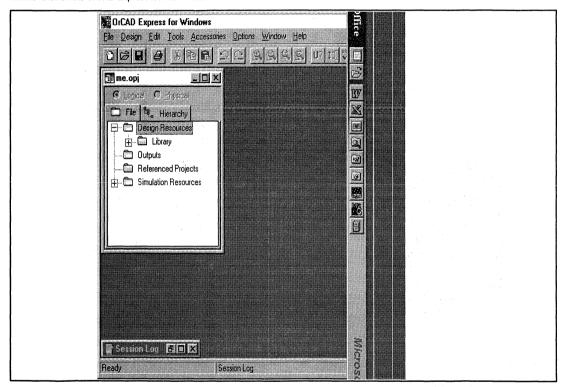

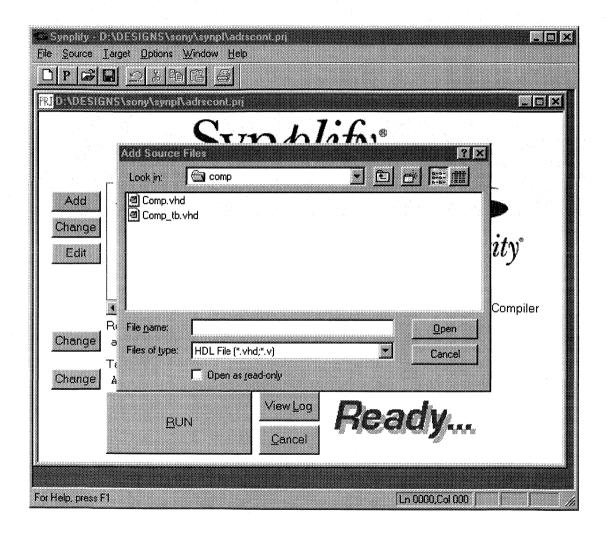

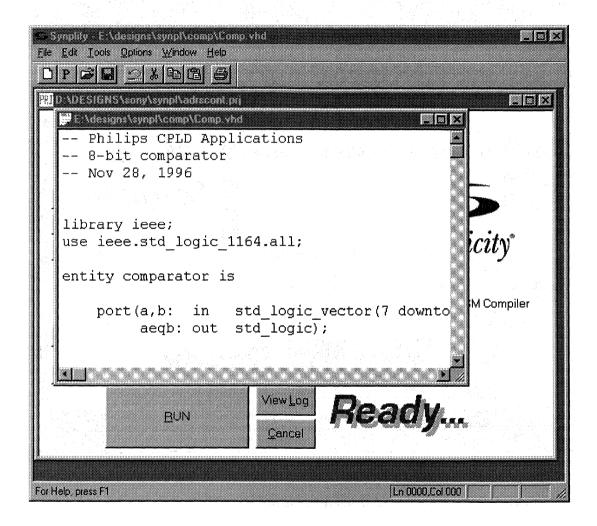

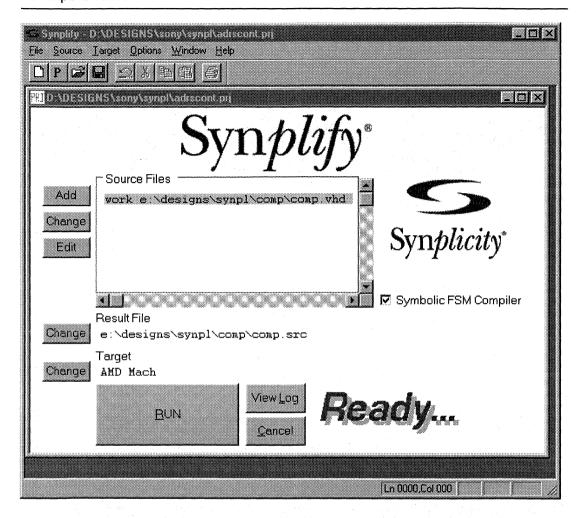

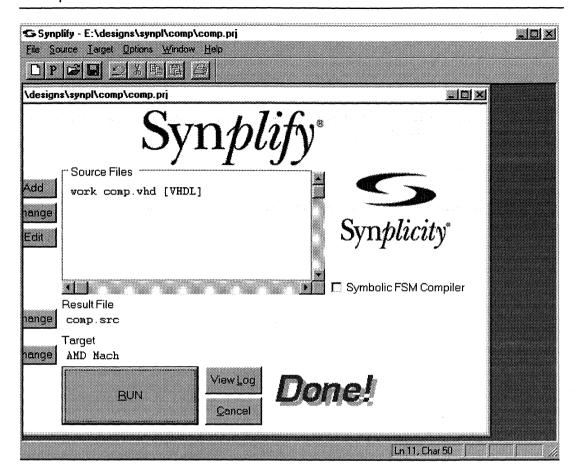

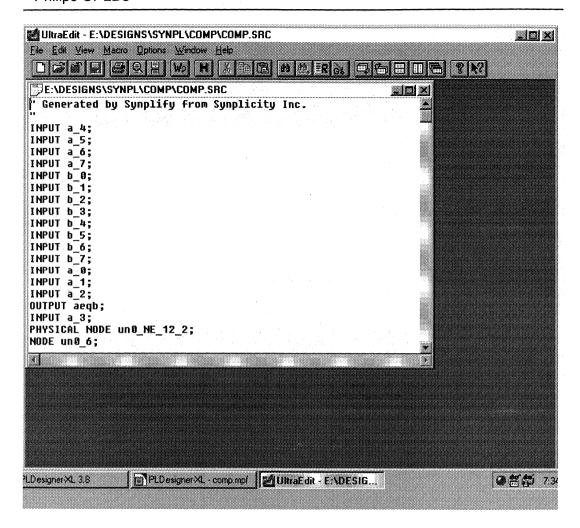

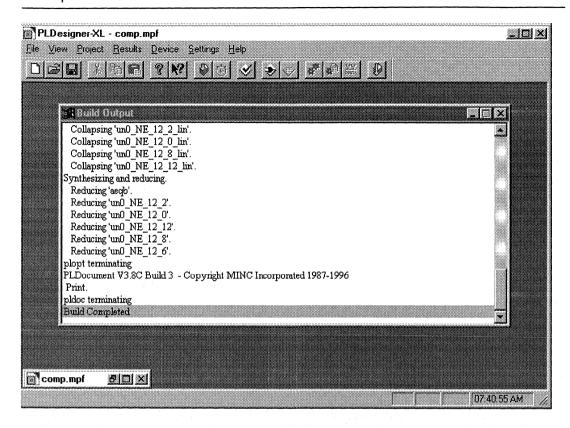

# Philips/Synopsys Design Environment

Philips CoolRunner CPLDs are supported in the Synopsys® design environment with the MINC Synopsys library interface for MINC's PLDesigner-XL. This interface includes the synthesis and simulation libraries for the Philips CoolRunner™ CPLDs, and describes the logic functions that may be used to implement designs in CoolRunner™ devices. Through the use of these libraries, VHDL or Verilog HDL design descriptions that target CoolRunner™ CPLDs can be entered in any of the following Synopsys tools: Synopsys Design Compiler family, Synopsys FPGA Compiler, and Synopsys Design Analyzer.

Design entry, simulation, and synthesis via the Synopsys design environment offers a number of advantages. In addition to simplifying the overall design task, the Synopsys tools support multiple HDLs with one compiler. As a result, there are no issues with language subsets or inconsistencies when moving between device architectures. The high-level, top-down Synopsys design environment increases productivity by providing a single front-end tool set for design, simulation, and synthesis of the overall system design. It also reduces development time for programmable logic devices by facilitating the re-use of designs previously developed in a Synopsys tool.

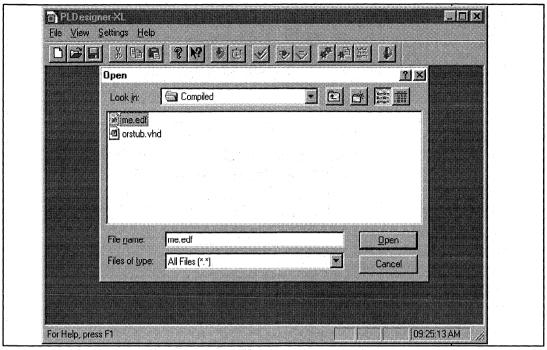

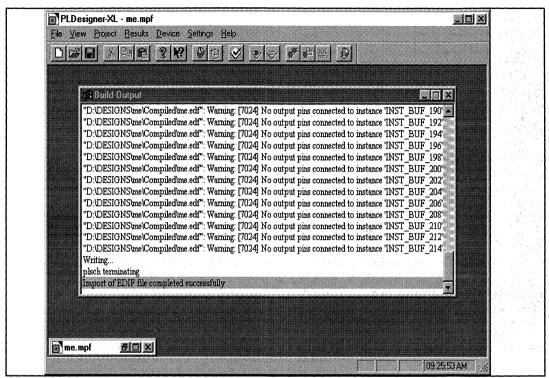

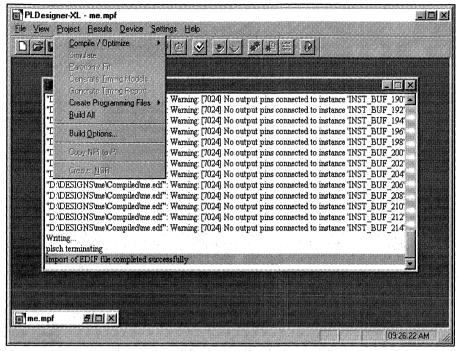

MINC's Synopsys library interface supports Philips CPLD's by targeting a library of MINC-specific components that includes the CoolRunner devices. This allows the designer to process a Synopsys design and generate an EDIF netlist that can, in turn, be read and processed by MINC's PLDesigner-XL. Within the PLDesigner-XL environment, the design can be further processed using all of the facilities this tool offers for physical implementation. This includes automatic, multiple device partitioning and fitting as well as device selection based upon the specification of multiple physical constraints, such as performance, power dissipation, and area.

### System and Software Requirements

- Synopsys Design Compiler (Version 3.5b) or FPGA Compiler (Version 3.5a)

- MINC's PLDesigner-XL

- Philips Device Libaries for MINC's PLDesigner-XL

### **Recommended Operating Systems**

- Hewlett-Packard HP-UX 9.05

- Sun MicroSystems SunOS 4.1.4 (V4.1.3 compatible)

- Sun MicroSystems Solaris 2.4 (requires SunOS compatibility mode)

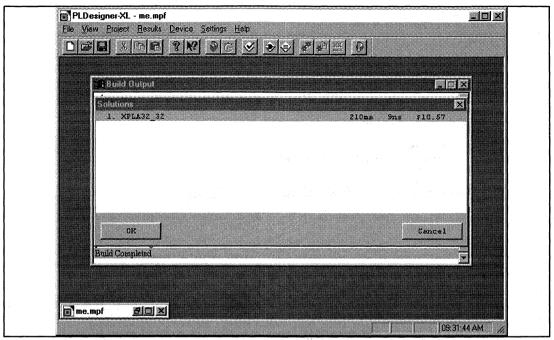

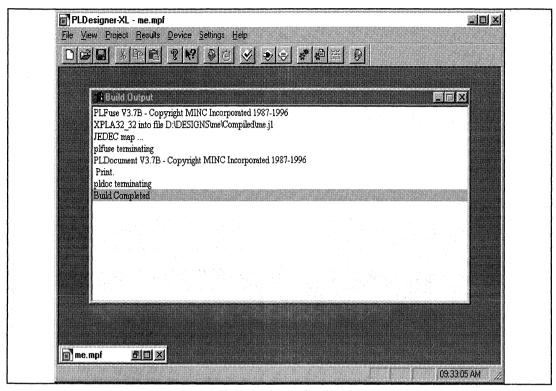

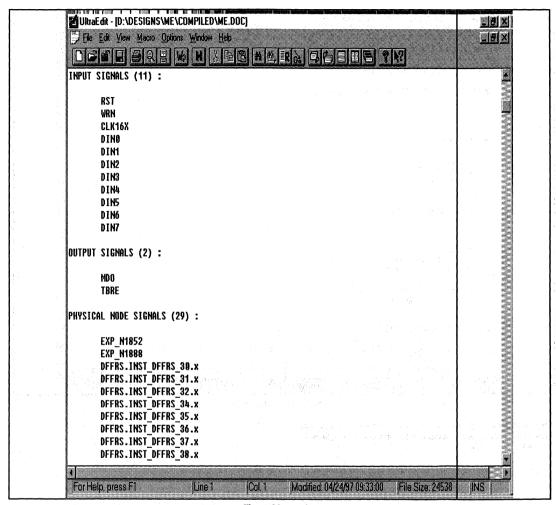

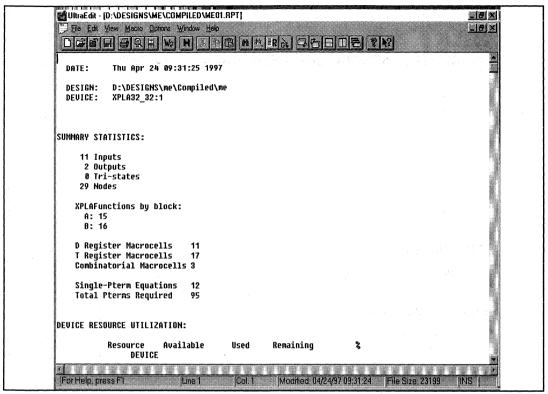

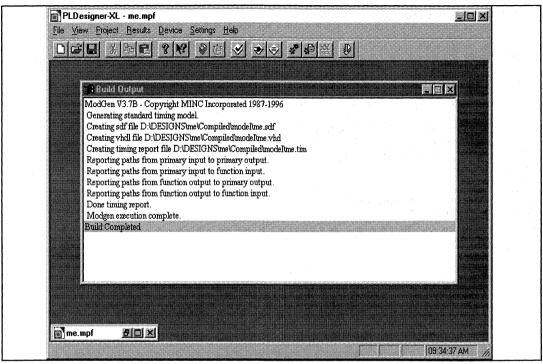

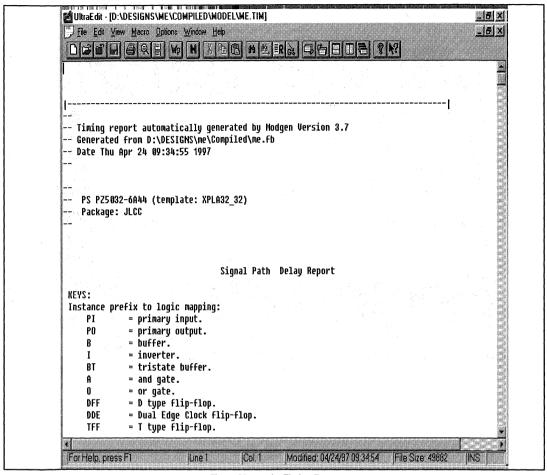

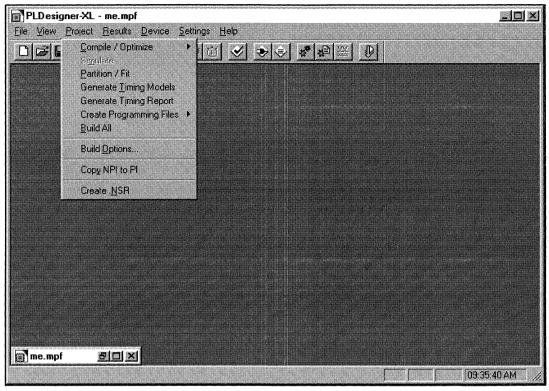

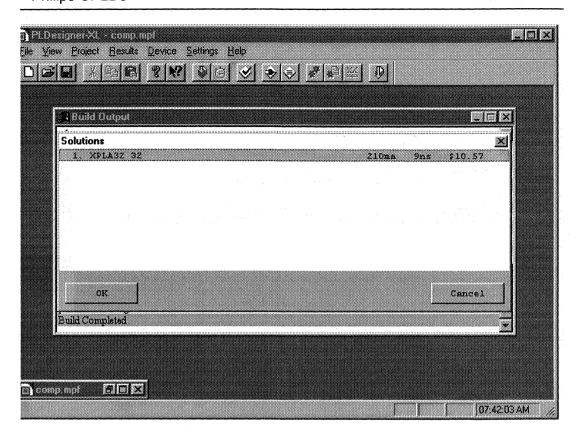

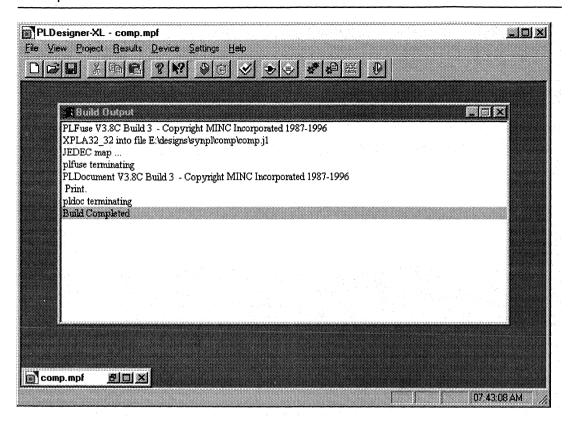

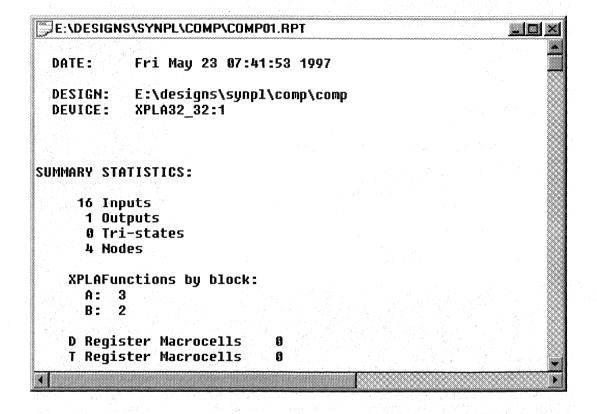

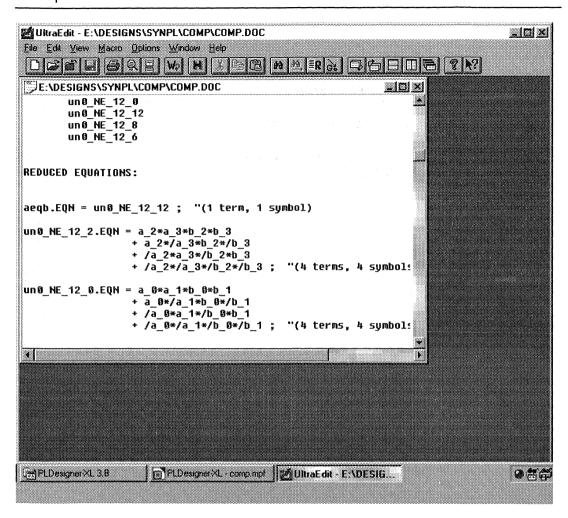

Figure 4.

33

1997 Apr 10

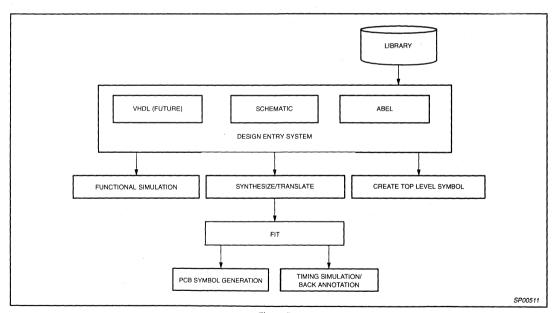

# Viewlogic/Philips Design Environment

The Phillips CPLD Fitter is fully integrated into the Intelliflow™/ViewPLD® products and Workview Office/Powerview design environments of Viewlogic. It is tightly integrated to work with the ViewDraw® design entry system, the ViewSynthesis® and ABEL synthesis, and the ViewSim® and SpeedWave™ simulation environments.

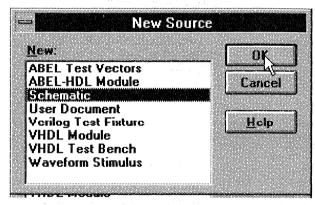

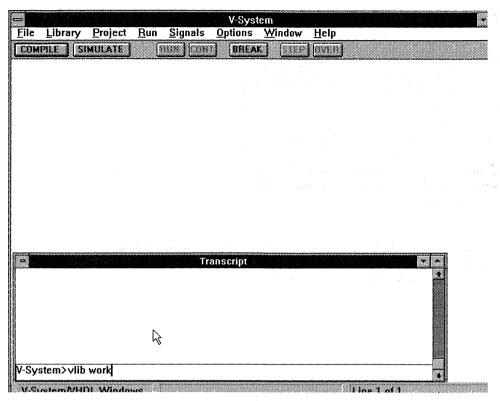

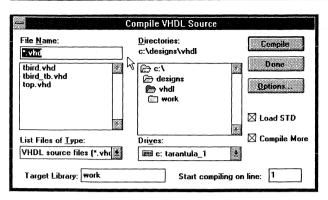

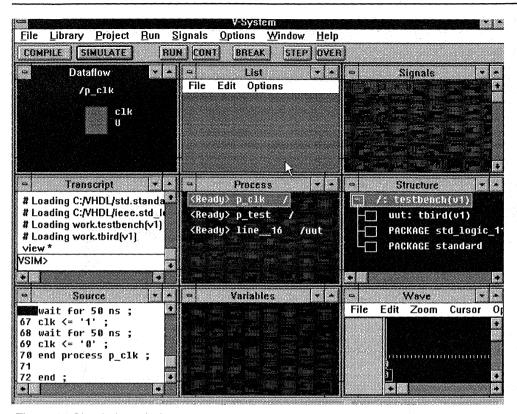

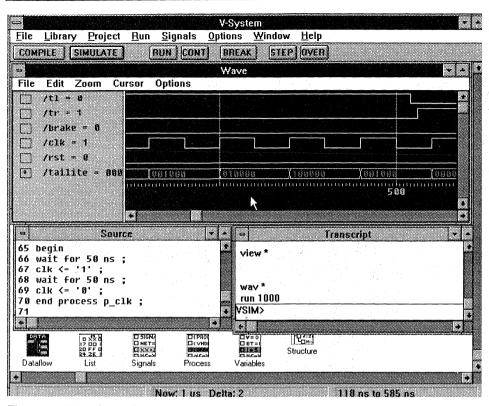

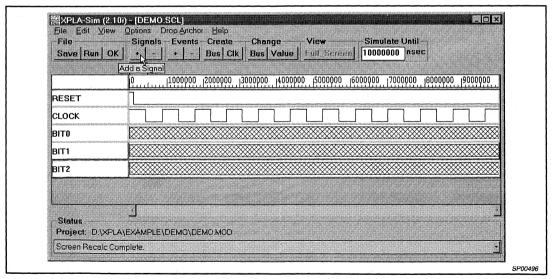

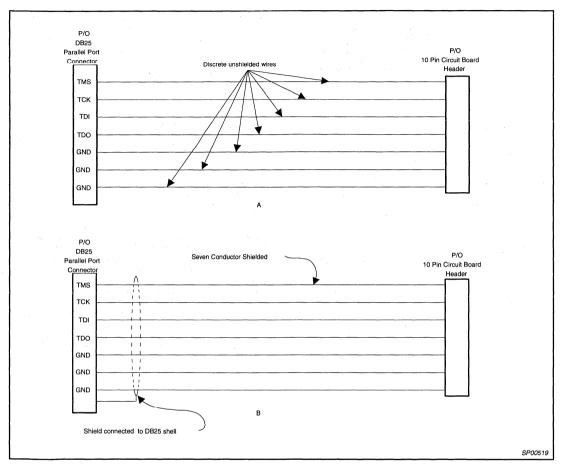

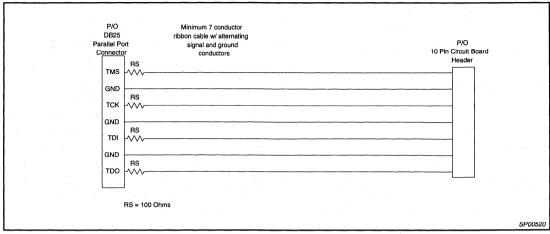

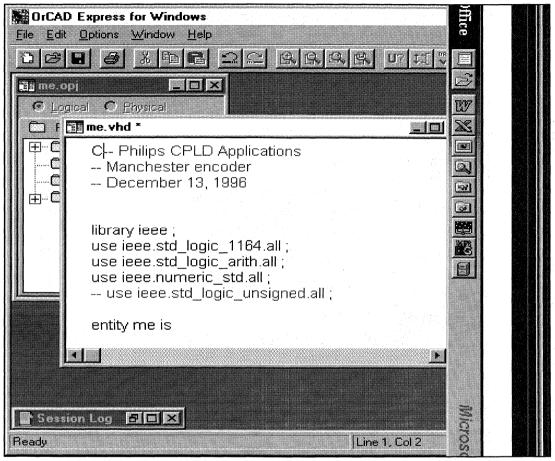

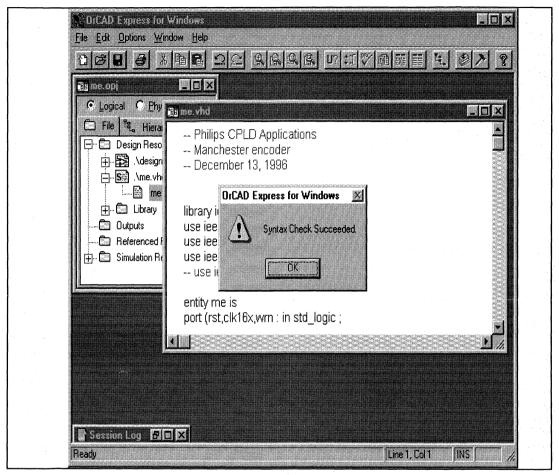

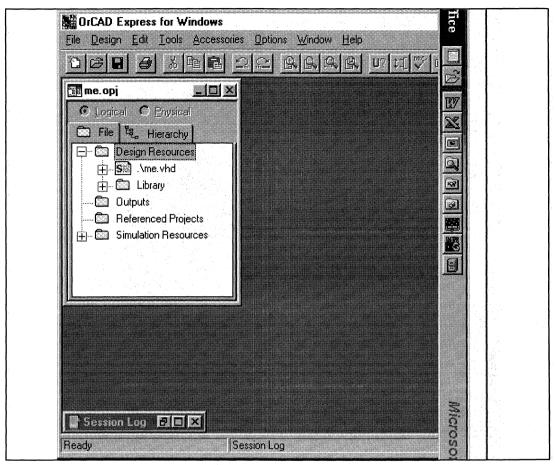

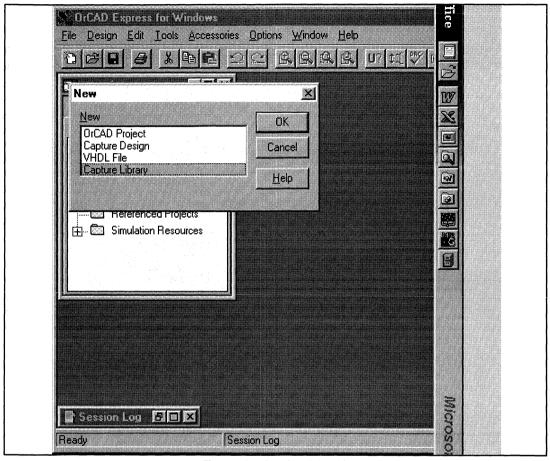

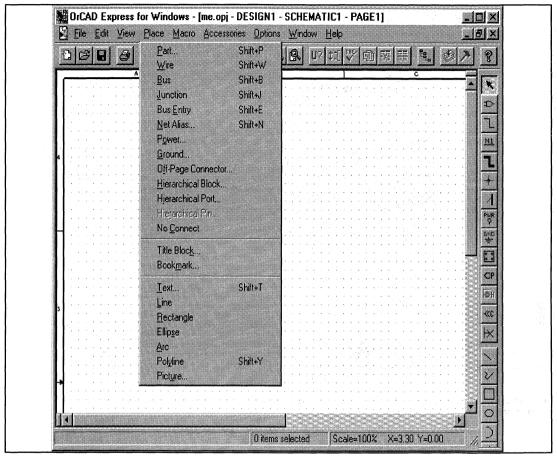

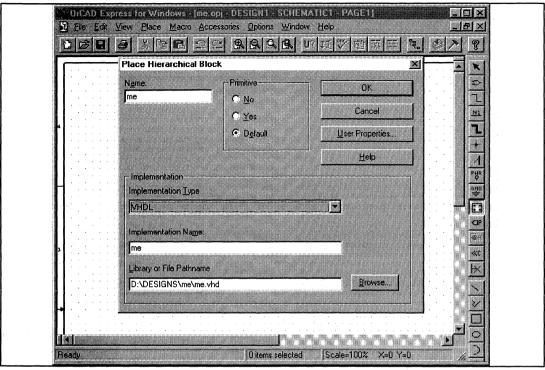

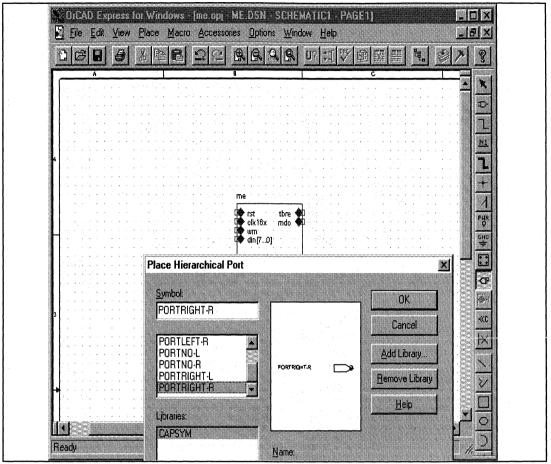

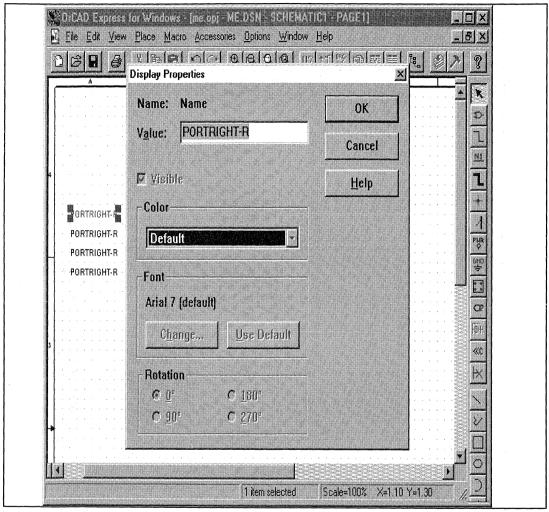

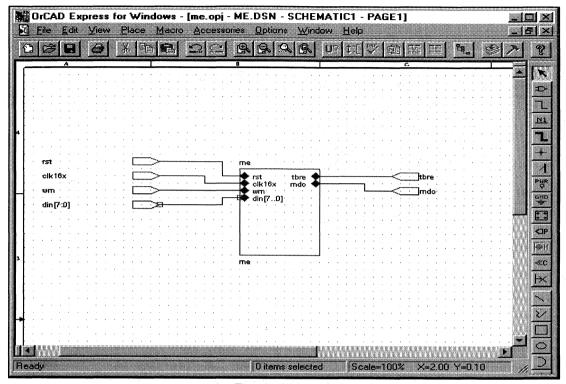

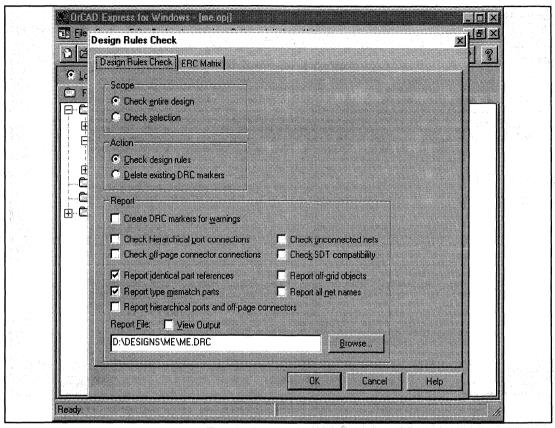

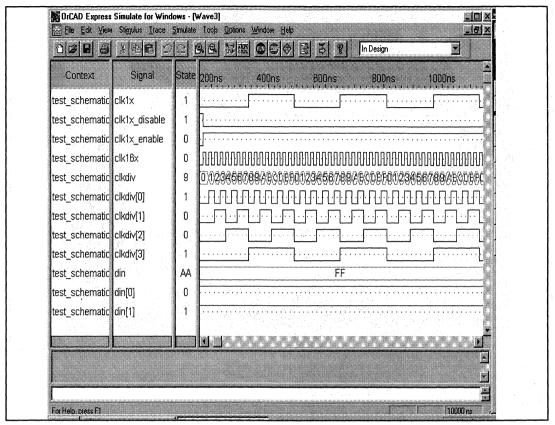

The Viewlogic/Philips design flow follows a top-down or mixed-level design methodology. Designs can be entered as schematics using ViewDraw or in the industry-standard hardware description languages, VHDL and ABEL. The design flow is flexible in that it allow users to enter designs as a mixture of schematic and hardware description language.